XtremeDSP解决方案将数字信号处理功能提升到极至

而且,拥有多达53,712逻辑单元、2,268 Kb BlockRAM、373 Kb分布式RAM、519个I/O引脚以及DeviceDNA安全技术和新的休眠/待机电源管理功能,Spartan-3A DSP器件提供了足够的信号处理容量,可以将价格/性能/功耗比降到更低水平。此外,基于FPGA的DSP解决方案所提供的设计灵活性以及快速上市时间进一步降低了风险,因此Spartan-DSP系列的价值变得越来越明显(参见表1)。

表1:Spartan-DSP平台填补了XtremeDSP产品线中的1-30 GMACS性能范围。

注意:1)在低速度级器件中。2)在高速度级器件中

将DSP性能提升到极限

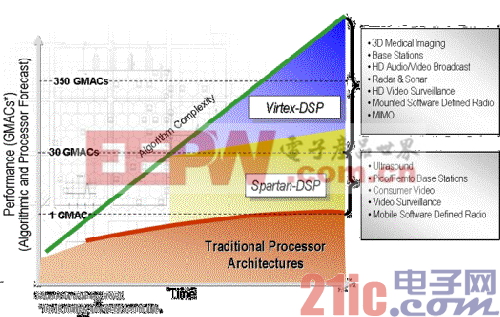

过去二十年里算法复杂性的快速提升是推动FPGA在DSP应用中使用的最重要市场动力。 固定架构的处理器如DSP和通用处理器(GPP)面临的问题是,固有的架构无效性使它们的性能限制在摩尔定律规定的理论限定值以下 .

此外,由于通信系统将数据传输效率不断推向香家定理(Shannon’s Law ) (参见图2)所限制的上限,里德-所罗门(Reed-Solomon)编码以及最近的Turbo码等高级技术也越来越靠近其理论极限,当然代价就是更高的计算复杂性。这就导致了算法性能要求和处理器性能之间的差距越来越大。因此,设计人员必须寻找新的设计解决方案(不局限于传统DSP范围),在固定结构处理器之外选择FPGA。

图 2.赛灵思FPGA填补算法复杂性和固定架构处理器无效性造成的性能差距

由于FPGA并行处理机制可提供极高性能的信号处理能力,因此非常适于来填补这一性能差距。FPGA灵活的架构使得可以方便地在相似系列器件之间进行设计移植,因此可以将标准甚至环境条件变化带来的风险降到最低。

DSP48E逻辑片

在XtremeDSP产品线所有器件中最有价值的资源之一就是DSP48逻辑片,它不仅帮助提升DSP设计的总性能,同时还可以提高实现所需要性能的设计和资源效率。DSP48是面向应用的组合模块(ASMBL™),可增强Virtex-DSP 和 Spartan-DSP器件中的DSP功能。这些DSP49逻辑片可帮助DSP设计人员设计出满足复杂挑战的解决方案,例如:成百上千的中频-基带下转换信道、3G扩频系统中的128X片码速处理、高分辨率H.264和MPEG-4编码/解码算法。

一个DSP48基本片(也称为 XtremeDSP基本片)包含两个DSP48逻辑片,构成通用粗粒度DSP架构的基础。DSP48逻辑片支持多种独立功能,包括乘法器、乘法-累加器(MACC)、加法乘法器、三端输入加法器、桶状移位寄存器、宽总线多路复用器、幅度比较器或宽输入加法器。不需要使用通用可编程逻辑构造资源,这一架构就可支持将多个DSP48 逻辑片连接起来完成更宽输入的数字功能、DSP滤波器和复杂算法。这可以带来更低的功耗、极高的性能和更高的芯片资源使用效率。

DSP逻辑片带来的另一项重要优点是可以从一个平台系列移植到另一个平台系列,例如,从Virtex-4 SX或Virtex-5 SXT 器件移植到Spartan-3A DSP器件。由于DSP48是Virtex-DSP和Spartan-DSP系列的基本DSP构造模块,因此从一个系列移植到另一个系列器件是很直接的过程,设计需要做的更改很小。

XtremeDSP设计工具

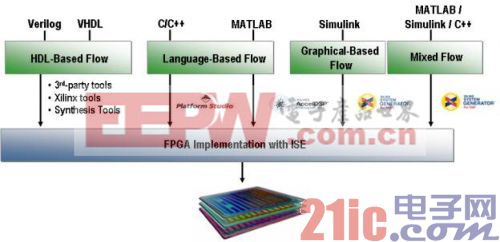

通过XtremeDSP计划,赛灵思及其第三方合作伙伴构成的业界生态系统达成了这样的共识,即将DSP的所有潜力和灵活性尽可能方便地提供给三类不同的设计人群:系统设计师、DSP工程师和FPGA/硬件工程师。每一类设计人员承担的职责不同(还有偏好),从而造成了他们对特定设计环境的要求不同。

系统设计师必须快速确定如何在可用的处理资源之间最好地划分不同的系统级功能。他们关注的重点是选择满足产品性能和吞吐能力要求的处理资源,同时满足尺寸、成本和功耗方面的预算。

图 3.XtremeDSP设计工具满足所有三类设计用户群体的设计环境要求(喜好)-系统设计师、DSP工程师和FPGA/硬件工程师

DSP工程师更关注DSP算法的创建和改进。他们通常不熟悉硬件设计细节,要依赖工具将细节抽象掉,这样他们才能够更专注于更高层的设计探索和验证。

硬件工程师通常采用VHDL 或 Verilog来从设计中获得最高的性能。他们通过需要在同一设计环境中与更高层功能模块以及自己的寄存器传输级(RTL)设计协同工作的能力,并且可以运行测试基准进行功能和性能验证。

因此XtremeDSP计划是否能够取得成功的一个关键标志就是在于设计工具满足所有三类设计群体的程度。XtremeDSP工具,如SystemGenerator for DSP 和 AccelDSP™ 综合软件提供了系统建模、算法开发和探索、自动生成测试基准向量、设计验证和调试以及HDL生成和仿真等功能。无论某个设计师是喜欢使用VHDL、Verilog、C/C++、MATLAB、Simulink和HDL,还是这些工具的任何组合,赛灵思的XtremeDSP工具都可以帮助他/她快速高效地充分发挥FPGA的所有潜力(参见图3)。

结论

FPGA填补了高性能应用对高性能DSP的需求与传统DSP处理器能够提供的性能之间巨大且不断增加的差距。有许多原因促使设计人员采用基于FPGA的DSP解决方案,其中四条最基本的原因归纳如下:

1. 处理极高的计算工作量 - FPGA支持工程师设计高度并行的架构,因此可支持与时钟频率相同的采样速率。系统因此可以保持高达500MSPS的高性能水平 – 适于构建超高速单通道系统或慢速率数百通道系统。

2. 从DSP处理器分流计算密集的任务,将宝贵的执行周期让给其它功能。

3. 定制适用于特定算法的架构 - FPGA提供的一系列MAC或乘法器可用于实现单抽头或多抽头的算法架构。FPGA的可重配置特点意味着工程师可以快速构建和修改设计架构。

4. 降低系统成本和功耗 - FPGA支持集成其它组件(如Serial RapidIO 收发器、PCI Express接口、胶合逻辑以及低速率控制任务),因此可以降低总体系统成本和功耗。此外,与传统DSP器件相比,并行机制提供了一个至几个数量级的性能优势,因此对于同样的性能,可以在更低的频率下工作。更低的频率可降低MOPS/mW(功效的最关键指标)。正如加州伯克利大学电子工程和计算机科学系Bob Brodersen教授所证明的,与当今的基准微处理器相比,FPGA的功率效率可高达其1000倍。(参看Bob Broderson的演示幻灯片)

评论