本节我们将对ucosII操作系统有个初步的认识,主要是从下面2个方面进行讲解:

1.UCOSII操作系统的简介

2.UCOSII操作系统组成部分

一、UCOSII操作系统的简介:

μC/OS-II 是一种基于优先级的抢占式多任务实时操作系统,包含了实时内核、任务管理、时间管理、任务间通信同步(信号量,邮箱,消息 队列)和内存管理等功能。它可以使各个任务独立工作,互不干涉,很容易实现准时而且无误执行,使实时应用程序的设计和扩展变得容易,使应用程序的设计过程大为减化。

关键字:

μC/OS-II 操作系统

引言

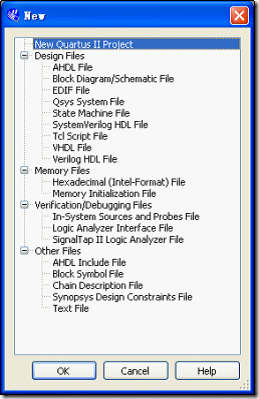

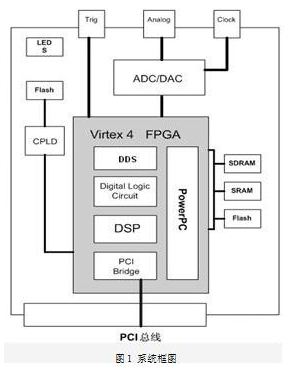

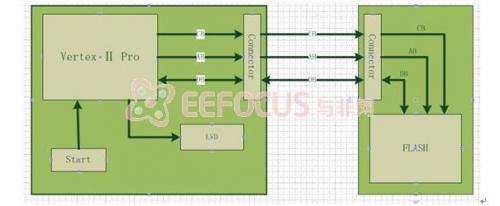

Altera公司的Nios II处理器是可编程逻辑器件的软核处理器。NiosII软核处理器和存储器、I/O接口等外设可嵌入到FPGA中,组成一个可编程单芯片系统(SOPC),大大降低了系统的成本、体积和功耗。适合网络、电信、数据通信、嵌入式和消费市场等各种嵌入式应用场合。

本文提出一个基于Nios II处理器结构的系统用于实现机器人实时运动检测跟踪,使用线性卡尔曼滤波器算法来快速完成运动估计及进一步分析和校正,算法中的乘除利用MATLAB/DSP Builder生成的模块作为Nios

关键字:

Nios II FPGA

Altera公司(Nasdaq: ALTR)宣布为其业界领先、成熟可靠的Quartus® II软件引入功能超级强劲的Spectra-Q™引擎,以提高下一代可编程器件的设计效能,缩短产品面市时间。Spectra-Q引擎的新功能创纪录地缩短了编译时间,提供通用、快速跟踪设计输入和置入式IP集成特性,延续了Altera Quartus II软件的领先优势,令基于FPGA和SoC的设计快马加鞭。现在,客户可以在更高抽象层面上进行设计并实现,极大地缩短了设计时间,解决了下一代设计面临的挑战。

关键字:

Altera Quartus II

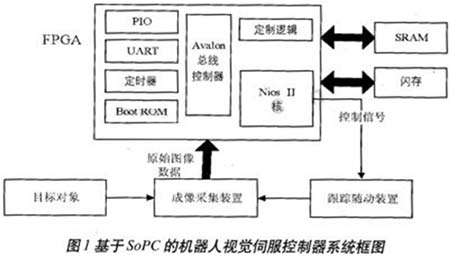

SOPC(System on a Programmable Chip,片上可编程系统)是Altera公司提出的一种灵活、高效的SOC解决方案。它将处理器、存储器、I/O接口、LVDS、CDR等系统设计需要的功能模块集成到一个可编程逻辑器件上,构建一个可编程的片上系统。它具有灵活的设计方式,软硬件可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。SOPC的核心器件FPGA已经发展成一种实用技术,让系统设计者把开发新产品的时间和风险降到最小。最重要的是,具有现场可编程性的FPGA延长了产品在市场的存

关键字:

SOPC DDS Nios II Altera

在嵌入式系统中为提高微型机系统的可靠性和安全性, 常用的方法就是使用“看门狗”。看门狗分硬件看门狗和软件看门狗。硬件看门狗采用“看门狗”电路, 通过定时器, 对微型机任务即“喂狗”在运行时间上加以约束, 任务必须在最大指定时间范围内完成, 否则重启系统。软件看门狗采用处理器内部定时器, 把任务的理论最大运行时间作为时间约束, 如果该任务超过了这个时间跨度, 则强制退出本次任务。上述看门狗采用的是单任务的顺序机制, 容易实现。在多任

关键字:

uC/OS-II LPC2132

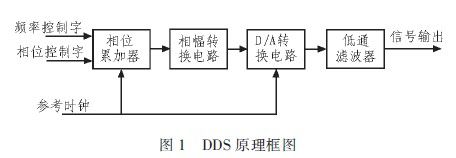

一、车辆调度系统的整体设计:

整个系统包括四个部分(1)通信主站;(2)车载从站;(3)通信链路。(4)系统监控部分。下面对各个部分的功能做一个简单的介绍。

(1)通信主站:完成信息的转发,它是连接系统监控部分和车载从站的纽带,它将从系统监控部分来的信息转发给车载从站。并且接收车载从站的信息,并将信息上传给系统监控部分。

(2)车载从站:被监控的对象,接收监控调度命令,并可以返回自己的状态信息。状态信息的取得是依靠在车载从站中的GPS接收机来完成车辆位置和速度信息等的采集工作。

关键字:

ARM7 UC/OS-II

引言

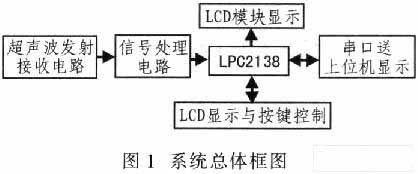

超声波指向性强,能量消耗缓慢,在介质中传播的距离较远,因而用于距离测量。利用超声波检测往往较迅速、方便、计算简单、易于实时控制,且测量精度能达到工业实用要求,因此在移动机器人的研制中得到广泛应用。移动机器人要在未知和不确定环境下运行,必须具备自动导航和避障功能。超声波传感器以其信息处理简单、速度快和价格低的特点广泛用作移动机器人的测距传感器,实现避障、定位、环境建模和导航等功能。

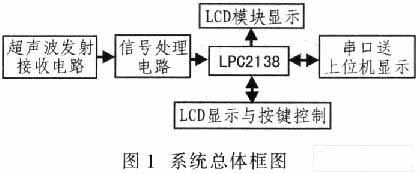

2 系统总体设计方案

2.1 超声波测距原理

2.1.1 超声波发生器

超声波为直线传

关键字:

LPC2138 μC/OS II

软件无线电的出现,是无线电通信从模拟到数字、从固定到移动后,由硬件到软件的第三次变革。简单地说,软件无线电就是一种基于通用硬件平台,并通 过软件可提供多种服务的、适应多种标准的、多频带多模式的、可重构可编程的无线电系统。软件无线电的关键思想是,将AD(DA)尽可能靠近天线和用软件来 完成尽可能多的无线电功能。

蜂窝移动通信系统已经发展到第三代,3G系统进入商业运行一方面需要解决不同标准的系统间的兼容性;另一方 面要求系统具有高度的灵活性和扩展升级能力,软件无线电技术无疑是最好的解决方案。用ASI

关键字:

FPGA Virtex-4 PowerPC

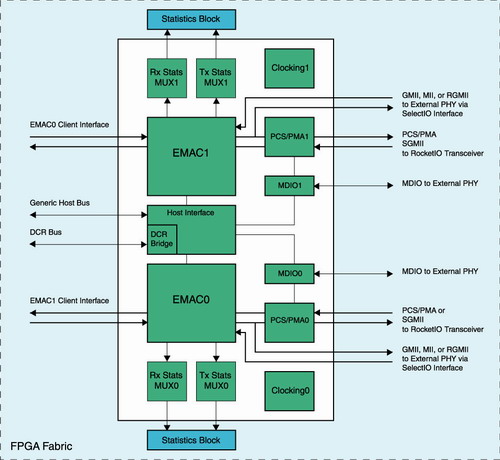

以太网是一个占据绝对优势的固线连接标准。Xilinx® Virtex™-5 以太网媒体接入控制器(以太网MAC)模块提供了专用的以太网功能,它和 Virtex-5 RocketIO™ GTP收发器以及 SelectIO™ 技术相结合,能够让用户与各种网络设备进行连接。在Virtex-5器件中,以太网MAC模块作为一个硬件块集成在FPGA内部。

在Xilinx设计环境中,以太网MAC是一个库原语,名为TEMAC。该原语包括一对10/100/1000 Mb

关键字:

Virtex-5 以太网

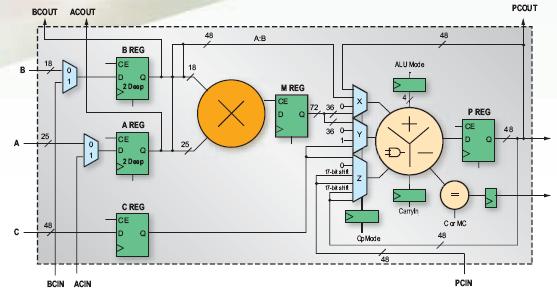

二十多年来,FPGA 为世人提供了最灵活、适应性极强、快速的设计环境。早期的 DSP 设计人员发现,可将一种可再编程的门海用于数字信号处理。如果把内置到 FPGA 架构中的乘法器、加法器和累加单元结合起来,就可以利用大规模并行计算实现有效的滤波器算法。

在未加工频率性能方面的损失,通过并行计算得到了弥补,而且得远大于失,可谓“失之东隅,收之桑榆”;由此获得的 DSP 带宽完全可与替代方案媲美。随着时间的推移,乘法器和加法器的实施越来越高效。1998 年,Xilinx 顺理

关键字:

Virtex-5 DSP

本文介绍Virtex - 5 FXT FPGA系列浮点接口,赛灵思logiCORE的IP处理器单元( APU )辅助PowerPC 440嵌入式微处理器设计的IP基础知识。

点击此处下载

关键字:

Virtex-5 FPGA

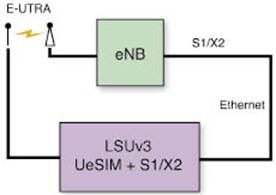

功能强大的可编程逻辑平台使得Prisma Engineering公司能够针对所有蜂窝网络提供可重配置无线测试设备。长期演进(LTE)是移动宽带的最3GPP标准,它打破了现有蜂窝网络的固有模式。LTE与前代UMTS和GSM标准相比,除采用高频谱效率的射频技术外,其架构还得到了大幅简化。LTE系统的无线接入部分Node-B,是连接无线电和整个互联网协议核心网络之间的边缘设备。这种架构无法监测和测试等效于UMTS中间链路上的元件。必须通过无线电接口,才能有效地测试LTE网络元件。

这正是Prisma

关键字:

Virtex-5 FPGA 仿真器

1 引言

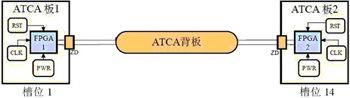

随着电子系统的不断发展,芯片间以及板间的数据传输需求也在不断增长,传统的单端并行数据传输模式早已不能满足现在高带宽应用的要求。USB 3.0、SATA 3.0、PCI-E 2.0等新串行规范的发布以及更高速的串并/并串转换单元(SERDES)芯片的推出更是引起了业界对高速差分串行数据传输的无限憧憬。为了解决下一代无线通信基站中多天线(MIMO)信号处理所带来的巨大数据吞吐量要求,本文基于Virtex-5 FPGA的GTP单元给出了一种在高级电信计算架构(ATCA)机箱内实现单对差分线进

关键字:

FPGA Virtex-5

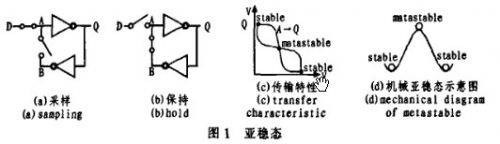

真随机数发生器(TRNG)在统计学、信息安全等领域有着广泛的应用。在这些领域中,不仅要求数据序列分布均匀、彼此独立,而且要求其具有不可预测性,能够抵御针对随机性的攻击。B.Sunar,W.J.Martin和D.R.Stinson提出,真随机数发生器的性能受3个因素的影响:熵源(Entropy Source),采集方式(Harvesting Mechanism)和后续处理(Post-Processing)。在电路系统中最常见的三种真随机数产生方法为:1)直接放大法:放大电路中的电阻热噪声等物理噪声,通过

关键字:

FPGA Virtex-5 随机数发生器

按照基于Windows的语言(C、C++、C#)等编程语言的初学入门教程,第一个历程应该是“Hello World!”的例程。但由于硬件上的驱动难易程度,此例程将在在后续章程中推出。硬件工程师学习开发板的第一个例程:流水灯,一切美好的开始。

本章将会在设计代码的同时,讲解Quartus II 软件的使用,后续章节中只讲软件的思想,以及解决方案,不再做过多的累赘描述。

一、Step By Step 建立第一个工程

(1)建立第一个工程,File-New-New

关键字:

FPGA Quartus II

virtex-ii介绍

您好,目前还没有人创建词条virtex-ii!

欢迎您创建该词条,阐述对virtex-ii的理解,并与今后在此搜索virtex-ii的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473