- 概述

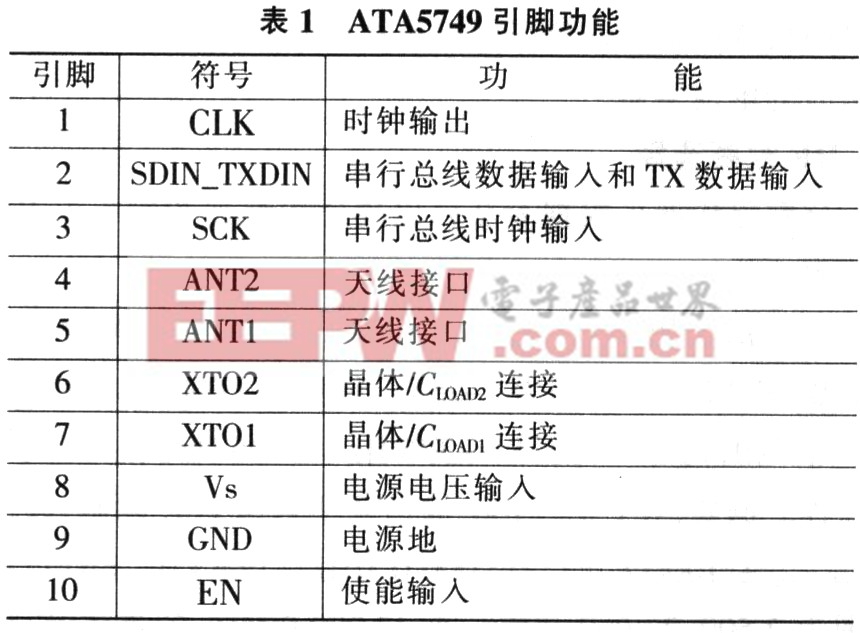

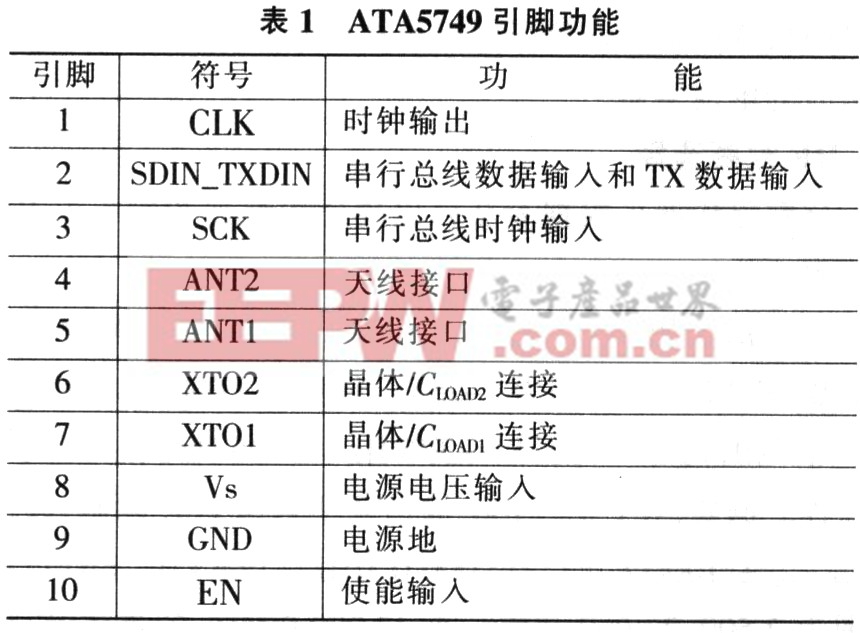

ATA5749是一款集成了完整小数分频器(fractional-N)的PLL射频发送器IC,适用于轮胎气压计、遥控无键入口和被动式入口汽车应用。ATA5749采用幅移键控(ASK)和闭环频移键控(FSK)调制,仅使用13.000 0 MHz晶体

- 关键字:

分频 应用 ATA5749 发送 集成 PLL 完全

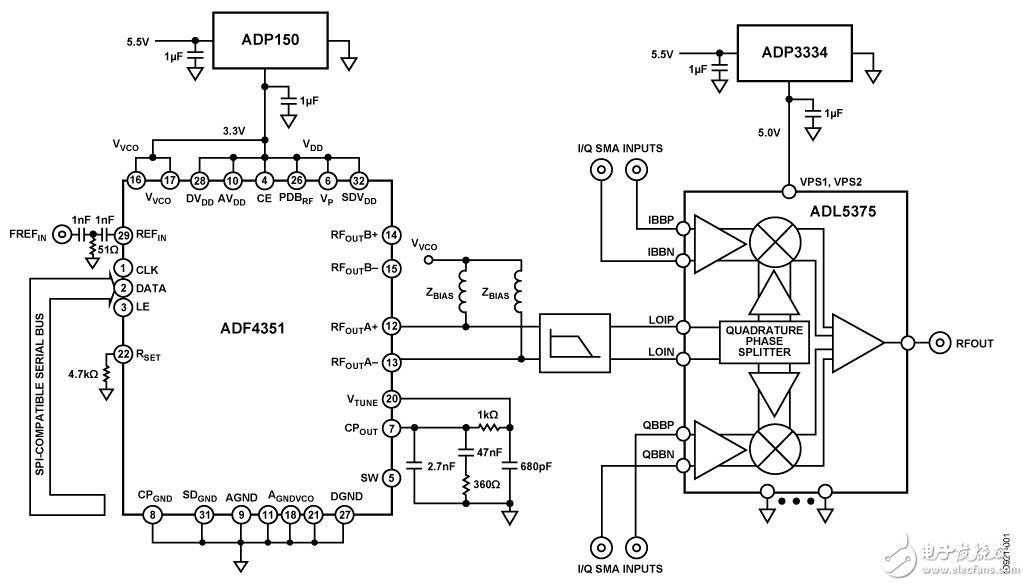

- 现代频率合成技术正朝着高性能、小型化的方向发展,应用最为广泛的是直接数字式频率合成器(DDS)和锁相式频率合成器(PLL)。介绍直接数字频率合成器和锁相环频率合成器的基本原理,简述用直接数字频率合成器(AD9954)和锁相环频率合成器(ADF4112)所设计的本振源的实现方案,重点阐述了系统的硬件实现,包括系统原理、主要电路单元设计等,并且对系统的相位噪声和杂散性能做了简要分析,最后给出了系统测试结果。

- 关键字:

DDS PLL

- 致力于丰富数字媒体体验、提供领先的混合信号半导体解决方案供应商 IDT® 公司(Integrated Device Technology, Inc.)推出其 VersaClock™ 计时器件的最新产品系列。VersaClock III 器件是专为高性能消费、电信、网络和数据通信应用设计的可编程时钟发生器,可以更经济有效地在多个晶体和振荡器之间进行选择。这些可编程计时解决方案对节省占板空间和保持功效非常关键,因其体积可能不允许全定制解决方案。多个具有各种不同需求的系统能够整合成更少的

- 关键字:

IDT VersaClock 可编程时钟发生器 PLL

- 摘 要:结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析和仿真,从仿真和测试结果

- 关键字:

DDS PLL 驱动 宽带频率

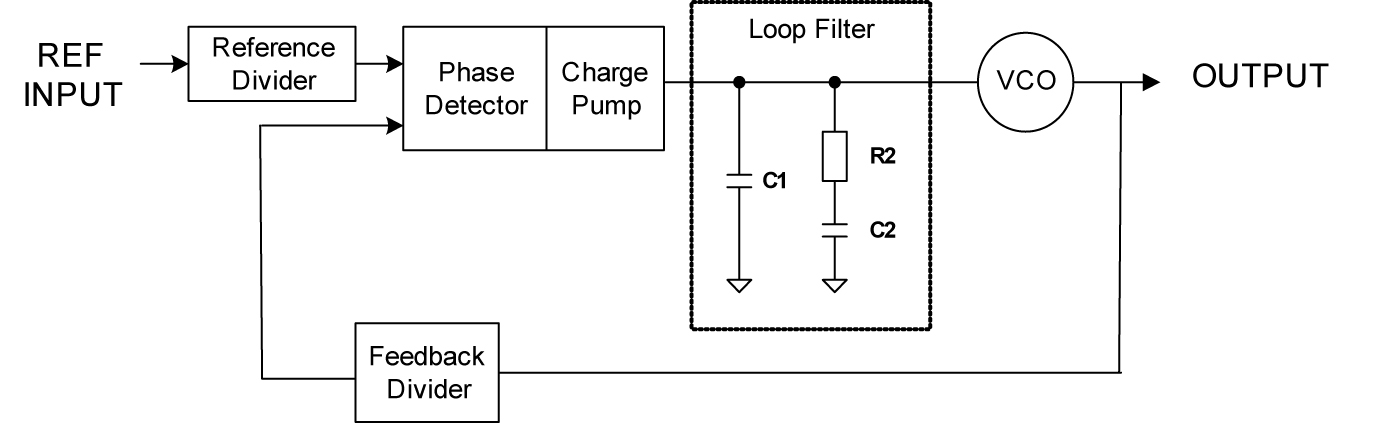

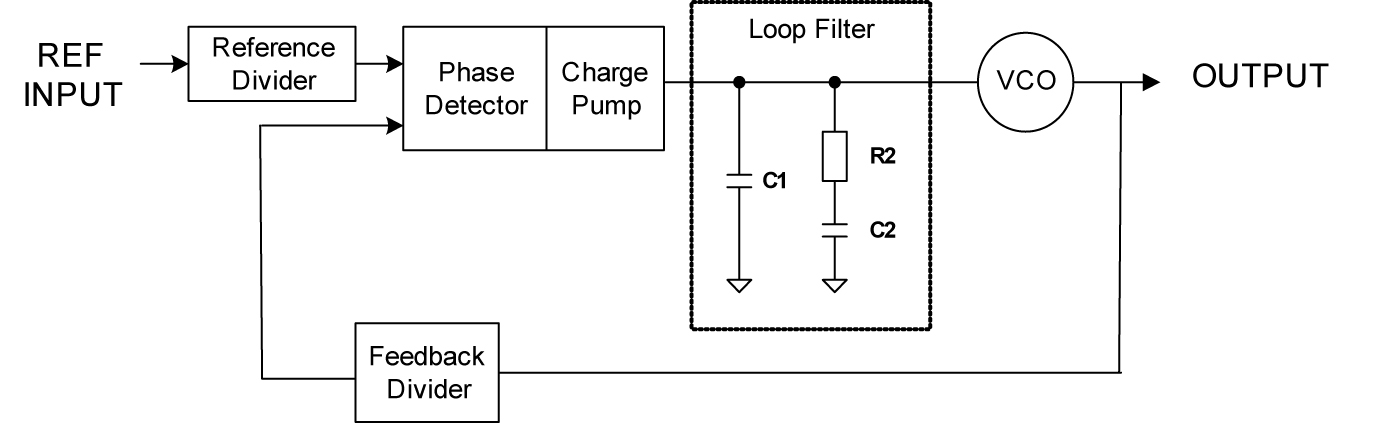

- 多年以来,作为业界主流产品的模拟PLL已被熟知,模拟PLL性能稳定,可为频率合成和抖动消除提供低成本的解决方案,工作频率高达8GHz及以上。然而新兴的基于直接数字频率合成(DDS)的数字PLL在某些应用中极具竞争力。本文比较了模拟PLL和基于DDS的数字PLL之间的差异,以及如何利用这些差异来指导设计人员选择最佳的解决方案。

数字PLL利用数字逻辑实现传统的PLL模块。虽然实现数字PLL的方法有很多,但本文只介绍基于DDS的数字PLL架构。

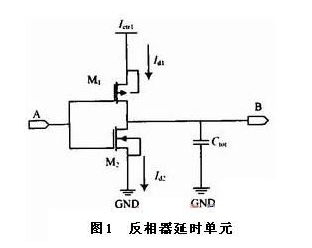

图1 典型的模拟PLL结构框图

- 关键字:

PLL DDS 分频器 鉴相器 DAC VCO

- 中国 北京——Analog Devices, Inc.(纽约证券交易所代码:ADI),全球领先的高性能信号处理解决方案供应商,最新推出一对时钟发生与分配IC——AD9520与AD9522,实现了业界最佳的器件集成度、低噪声、低抖动性能与信号输出灵活性的完美组合。 AD9520与AD9522多输出时钟发生器内置一个512 Byte的嵌入式EEPROM存储器模块,为系统工程师提供了可用作时钟源和系统时钟的双重可编程时钟解决方案。通过利用片上存储器对具体的输出

- 关键字:

EEPROM 冗余基准 PLL Analog Devices

- Maxim推出基于晶体的锁相环(PLL) VHF/UHF发送器MAX7057,能够在较宽的频率范围内发送OOK/ASK/FSK数据。器件配合适当的晶体频率,可以发送300MHz至450MHz范围内的任何信号,并能够以高达100kbps的速率发送NRZ码(50kbps曼彻斯特码)。

MAX7057集成了可编程分数N PLL合成器和宽带VCO,因而具有极大的灵活性。此外,还可以设置内部电容,实现功率放大器(PA)与天线之间的阻抗匹配。这种拓扑结构可确保多个工作频率下的高效率传输,从而使MAX7057

- 关键字:

Maxim PLL 锁相环 发送器

- CDCE937 和 CDCEL937 均为基于 PLL 模块的、低成本、高性能的可编程时钟合成器,可以在单输入频率的不同频率下生成多达七个输出时钟。每一个输出均可以进行系统内编程,从而使用三个独立的可配置 PLL 就可用于任何高达 230MHz 的时钟频率。该器件具有简单的频率同步,使零-PPM 时钟生成成为可能。另外,这两种合成器还具有扩频时钟及片上 EEPROM 和通过 SDA/SCL 进行系统内热编程的特点。对于数字媒体系统、流媒体、GPS 接收机、便携式媒体以及DSP/OMAP/DaVinci

- 关键字:

TI 时钟合成器 可编程 PLL

- 0 引 言

目前,脉冲雷达的脉内信号分析一直是研究的热点和难点,如何能更快速,准确的对脉内载波频率测量成为研究人员关注的目标,与此同时高精度频率源在无线电领域应用越来越广泛,对频率测量设备有了更高的要求,因此研究新的测频方法对开发低成本、小体积且使用和携带方便的频率测量设备有着十分重要的意义。本文根据雷达发射机频率快速变化的特点,采用目前新型的逻辑控制器件研究新型频率测量模块,结合等精度内插测频原理,对整形放大后的脉冲直接计数,实现对下变频后单脉冲包络的载波快速测频。具有测量精度高,测量用时短的

- 关键字:

测频模块 时钟内插 时钟移相 PLL 脉内测频

- 特瑞仕半导体株式会社开发了XC25BS8系列内置分频、倍频电路超小型PLL时钟发生器。

XC25BS8系列是能在低频输入8kHz、4095倍的范围内倍频工作的PLL时钟发生器IC。

输入端分频因子(M)可从1~2047的分频范围内进行选择;输出端分频因子(N)可从1~4095的分频范围内进行选择。输出频率在1MHz~100MHz的范围内,输入时钟为8kHz~36MHz的标准时钟。在内部可进行微调,在少量外置部件的条件下动作。从CE端子输入低电平信号,可停止整个芯片动作,抑制

- 关键字:

半导体 特瑞仕 时钟发生器 PLL

- 全球领先的高能效电源半导体解决方案供应商安森美半导体(ON Semiconductor,美国纳斯达克上市代号:ONNN)扩充了高性能时钟和数据管理产品系列,推出九款基于锁相环(PLL)的新PureEdge™时钟模块,替代晶体振荡器(XO)。NBXxxxx系列非常适用于高速网络、电信和高端计算应用。

安森美半导体亚太区标准产品部市场营销副总裁麦满权说:“安森美半导体新的时钟模块标志着公司进入频率控制市场,以充分发挥我们公司在高性能、超低抖动时钟分配领域奠定的长期领先地位。这

- 关键字:

安森美半导体 PureEdge PLL

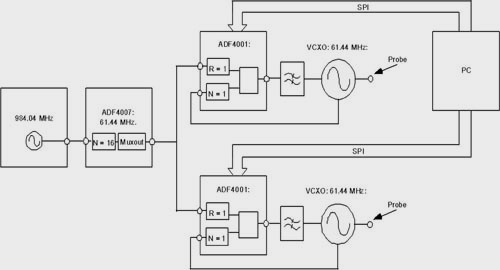

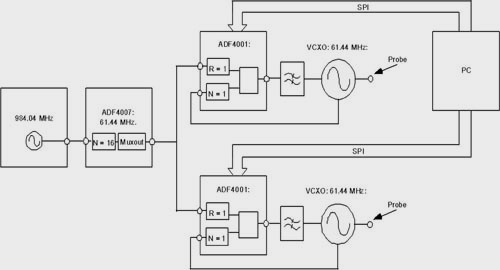

- 锁相环(PLL)广泛应用于无线通信,在基站中的主要用途是为发射器和接收器中的上变频和下变频电路提供一个稳定的、低噪声的射频(RF)本地振荡器(LO)。鉴于PLL本身的性能,它还可以用于控制其他许多电路中时钟信号的定时,而且在某些应用中,如果使用得当可以代替价格较贵的定时芯片。

大多数高速数字电路的设计工程师会在注重相位的应用中选择很贵的定时芯片,因为通常都是对限定频率范围(通常是适合SONET/SDH频率的线路速率)粗略地表征定时指标。相比之下,PLL器件通常覆盖了很宽的频率范围,而且在相位控制

- 关键字:

锁相环 PLL

- 在所有电子系统中,时钟相当于心脏,时钟的性能和稳定性直接决定着整个系统的性能。典型的系统时序时钟信号的产生和分配包含多种功能,如振荡器源、转换至标准逻辑电平的部件以及时钟分配网络。这些功能可以由元器件芯片组或高度集成的单封装来完成,如图1所示。

系统时钟源需要可靠、精确的时序参考,通常所用的就是晶体。本文将比较两种主要的时钟源——晶体振荡器(XO,简称晶振)模块和锁相环(PLL)合成器,并探讨高性能PLL的发展趋势。

图1:安森美半导体提供的

- 关键字:

时钟源 选择 PLL 发展

- 在所有电子系统中,时钟相当于心脏,时钟的性能和稳定性直接决定着整个系统的性能。典型的系统时序时钟信号的产 ...

- 关键字:

振荡 锁相环 PLL 同步 缓存 倍频 动态

- 介绍分频锁相频率合成技术。通过对锁相环工作过程及相位噪声等的基本原理的分析,采用PLL技术成功设计了1.8 GHz锁相频率源。

- 关键字:

PLL 合成 频率源

spf-pll介绍

您好,目前还没有人创建词条spf-pll!

欢迎您创建该词条,阐述对spf-pll的理解,并与今后在此搜索spf-pll的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473