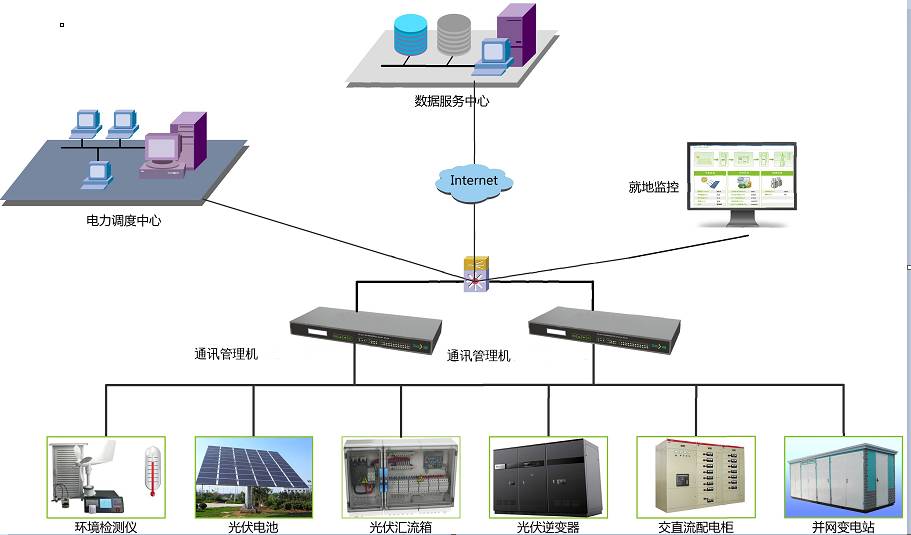

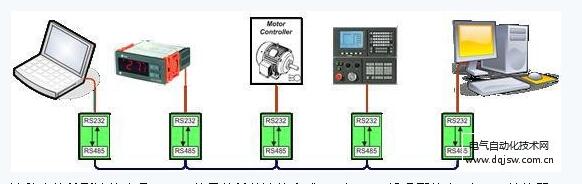

工业现场常同时用隔离RS-232和RS-485,常规方案是用两个隔离DC-DC配合信号隔离电路设计。ZLG的MPM集成RS-232和RS-485接口,电源、RS-232、RS-485之间相互隔离,可简化类似的应用。下面以通讯管理机为例说明。 通讯管理机的接口电路简述 通讯管理机在电力系统中可以采集多个子系统的数据,通过集中处理和回执,完成电力系统中的数据交互。对外通常需要集成多路RS-232、RS-485、CAN、以太网接口等。

图1 通讯管

关键字:

RS-232 RS-485

PCI Express是从PCI发展而来的一种系统互联接口标准。PCI和PCI-X都是基于32位以及64位的并行总线,而PCI Express则使用高速串行总线。PCI Express后向兼容于PCI,能够灵活地提供大峰值带宽。

关键字:

PCIExpress PCI FPGA

如图 2 所示,即 PCI Express 的层次体系结构。它保持了与 PCI 寻址模式(加载-存储体系结构且具有单层地址空间)的兼容性,从而保证了所有现有的应用程序和驱动操作无需改变

关键字:

PCIExpress PCI

本白皮书主要着眼已经得到广泛采用的PCI 总线的成功优势所在,同时详细介绍下一代高性能I/O 互连技术PCI Express 它将作为标准的局域I/O 总线被广泛应用于未来各种计算机平台

关键字:

PCI PCIExpress

Altera 的 MAX® II CPLD 系列自从推出以来,在低功耗应用上大展身手,特别是新的零功耗 MAX IIZ ,它的动态功耗和待机功耗都是业界最低的。 Altera新的零功耗 MAX IIZ CPLD ,在 CPLD 业界实现了最低的静态和动态功耗。 Altera® CPLD 能够帮助您提高性能,同时降低功耗。

关键字:

Altera 低功耗 MAXII CPLD

经过几十年的发展,全球各大开发商和供货商都开发出了多种可编程逻辑器件 . 比较典型的就是 Xilinx 公司的 FPGA 器件和 Altera 公司的 CPLD 器件系列,他们开发较早,占有大部分市场?在欧洲用 Xilinx 的人多,而 Altera 公司占有日本和亚太地区的大部分市场,在美国则是平分秋色。

关键字:

Xilinx Altera 芯片 选型 CPLD

Altera公司宣布,开始批量发售Cyclone IV FPGA。公司还宣布开始提供基于Cyclone IV GX的收发器入门开发套件。Altera的Cyclone IV FPGA设计用于无线、固网、广播、工业和消费类市场等低成本、小型封装应用。与前一代Cyclone产品相比,这些器件前所未有的同时实现了低成本和高性能,功耗降低25%,满足了大批量低成本串行协议解决方案的需求。

关键字:

Cyclone Altera IVFPGA

Altera低功耗28-nm器件的优点包括,降低产品成本,降低或者放宽功耗预算,较低的散热要求,能够满足更多的市场需求,在同样的散热和功耗预算内进一步提高性能等。采用最全面的方法降低28-nm产品的功耗,Altera帮助设计人员满足了迫切的低功耗需求。

关键字:

Altera 28nm FPGA

随着信息技术的发展,基于微处理器的数字信号处理在测控、通讯、雷达等各个领域得到广泛的应用。被处理的模拟信号也在向高频、宽带方面发展,但这需要高速、高分辨率的数字采集卡以将模拟信号数字化。美国国家半导体公司新推出的系列高速、高分辨率模/数转换器(如CLC5958)就非常适用于需要高速、高分辨率的信号采集系统。

关键字:

CLC5958型 A/D转换器 FPGA PCI

本节旨在通过给定的工程实例——“蜂鸣器播放梁祝音乐”来熟悉Altera Quartus II软件的基本操作、设计、编译及仿真流程。同时使用基于Altera FPGA的开发板将该实例进行下载验证,完成工程设计的硬件实现,熟悉Altera FPGA开发板的使用及配置方式。

关键字:

Cyclone Altera FPGA QuartusII FPGA最小系统

FPGA最小系统是可以使FPGA正常工作的最简单的系统。它的外围电路尽量最少,只包括FPGA必要的控制电路。一般所说的FPGA的最小系统主要包括:FPGA芯片、下载电路、外部时钟、复位电路和电源。如果需要使用NIOS II软嵌入式处理器还要包括:SDRAM和Flash。一般以上这些组件是FPGA最小系统的组成部分。

关键字:

FPGA最小系统 Altera NiosII Flash SDRAM

本文提出了一种基于Altera SOPC技术的总线桥接通信模块设计方法,完成1553B总线到PCI总线的桥接功能。在Altera FPGA平台上,自主设计了1553B总线控制模块,由Altera提供的IP核生成PCI总线控制模块,通过Nios II处理器完成总线数据交互。整个系统仅由一块FPGA和1553B总线的通信驱动电路组成,实现了系统的最小化设计。

关键字:

SOPC技术 总线桥接通信 1553B-PCI

pci-altera-485介绍

您好,目前还没有人创建词条pci-altera-485!

欢迎您创建该词条,阐述对pci-altera-485的理解,并与今后在此搜索pci-altera-485的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473