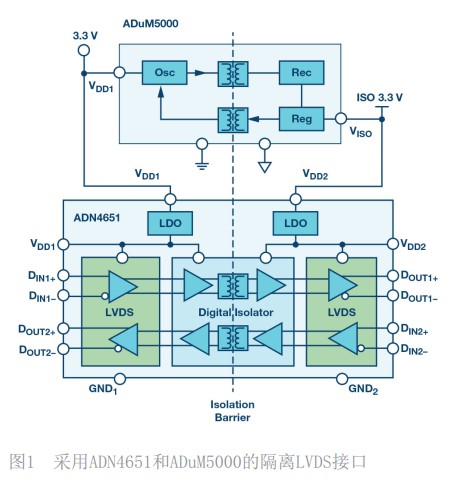

- 介绍了高速信号传输的挑战,及ADI公司的信号隔离式LVDS缓冲器——ADN4650/ADN4651/ADN46521是,若与ADuM5000组合使用,可实现短距离600 Mbps和数米距离200 Mbps的传输速率。

- 关键字:

数字隔离 LVDS 接口 201902

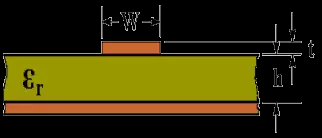

- 没有阻抗控制的话,将引发相当大的信号反射和信号失真,导致设计失败。常见的信号,如PCI总线、PCI-E总线、USB、以太网、DDR内存、LVDS信号等,均需要进行阻抗控制。阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。 不同的走线方式都是可以通过计算得到对应的阻抗值。 微带线(microstrip line) •它由一根带状导线与地平面构成,中间是电介质。如果电介质的介电常数、线的宽度、及其与地

- 关键字:

PCB LVDS

- 据业内人士透露,三星电子几乎订购了中国LED外延片和芯片制造商三安光电位于厦门的Mini LED产能,以确保其将在2018年第三季度推出的大尺寸高端液晶电视背光芯片供应。

消息人士称,三星已经为此次芯片供应预付了1683万美元。

中国LED芯片制造商华灿光电和厦门乾照光电也已开始了MicroLED和Mini LED技术的研发,而中国的LED封装服务提供商佛山国星光电则于2018年3月初设立了MicroLED和Mini LED研究中心,以便在2020年能够封装0.5-1.0mm的Mini

- 关键字:

三安光电 Mini LED

- 根据TrendForce光电研究最新“新型显示技术成本”报告,由于Mini LED作为LCD背光的架构与现行LCD显示器的LED背光架构相仿,在设计上并无太大改变,因此也被厂商寄予厚望,希望其可成为Micro LED量产前的过渡产品。但不论是手机或电视等消费性电子产品,Mini LED势必将直接面对来自OLED的竞争,短期而言,大尺寸电视及高阶IT产品是Mini LED有机会与OLED一较高下的应用领域。

以电视来看,WitsView指出,由于OLED的印刷上色技术尚未成

- 关键字:

Mini LED OLED

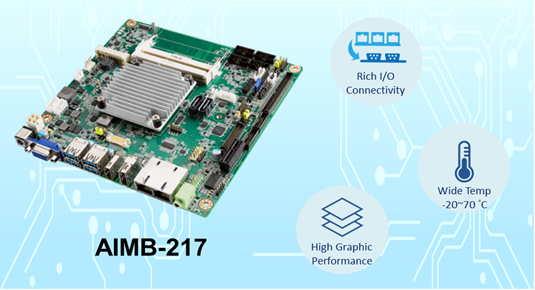

- 全球智能系统产业的领导厂商研华科技今天发布新型工业级无风扇超薄Mini-ITX主板AIMB-217。该产品搭载最新Intel® Pentium®、Celeron®和Atom® N4200/N3350/x7-E3950处理器(ATOM第六代Apollo Lake),相较于上一代产品而言CPU性能和显示性能分别实现了30%和45%的显著提升。同时,AIMB-217还捆绑研华专属WISE-PaaS/RMM软件套件,可实现远程设备管理。 AIMB-217的显示性能已提升

- 关键字:

研华 Mini-ITX

- 如何用单个赛灵思FPGA数字化数百个信号- 在新型赛灵思 FPGA 上使用低电压差分信号(LVDS),只需一个电阻和一个电容就能够数字化输入信号。由于目前这一代赛灵思器件上提供有数百个 LVDS 输入,理论上使用单个 FPGA 就能够数字化数百个模拟信号。

- 关键字:

赛灵思 FPGA LVDS

- 数字电视的发展,使人们对各种高画质影音设备的购买需求激增。FPD TV、DVD播放器、NB、数字相机及数字摄影机都已出现支持Full HD规格的产品。

- 关键字:

LCD LVDS IC

- 高速串行互连是标志并行数据总线向串行总线转变的技术里程碑,这种技术是减少设计师面临的信号阻塞问题的方法。这种转变是由业界对系统成本和系统扩展能力的要求所推动的。随着芯片技术的发展和芯片尺寸的缩小,用速率达数千兆位的高速串行互连来取代传统的并行结构变得简单易行。

- 关键字:

差分信号技术 LVDS FPGA

- 红外成像导引头采用红外焦平面阵列探测器,易受太阳光等杂散光的影响,评估杂散光对红外探测器成像质量的影响十分重要。由于导引头输出的信号一般采用LVDS或HOTLink格式传输,不能被杂散光测试设备直接接收,设计了一种图像调理卡,采用FPGA为控制核心,将红外探测器输出的图像信号进行格式转换和调理后传输至杂散光测试设备。

- 关键字:

导引头 LVDS FPGA

- JESD204B接口是一个串行解串器链路规范,允许12.5Gbps的最大数据速率传输。使用高级工艺(例如65nm或更小)的转换器支持该最大数据速率,还可提高电源效率。系统设计人员可充分利用该技术相对于低压差分信号(LVDS)DDR的优点

- 关键字:

数据转换器 JESD204B LVDS PHY模式

- 摘要 网络下载器作为航天计算机地面检测系统的重要组成部分,发挥着重要的作用。文中主要介绍了网络下栽器的总体设计思路,给出了硬件模块的设计原理图。并在PCB设计中,对于LVDS接口、高速总线以及叠层的设计中给出

- 关键字:

LVDS 通用下载器 FPGA

- 现场可编程门阵列(FPGA)与模数转换器(ADC)输出的接口是一项常见的工程设计挑战。本文简要介绍各种接口协议和标准,并提供有关在高速数据转换器实现方案中使用LVDS的应用诀窍和技巧。接口方式和标准现场可编程门阵列

- 关键字:

FPGA ADC LVDS JESD204 接口方式

- 摘要:超高速ADC通常采用LVDS电平传输数据,高采样率使输出数据速率很高,达到百兆至吉赫兹量级,如何正确接收高速LVDS数据成为一个难点。本文以ADS42LB69芯片的数据接收为例,从信号传输和数据解码两方面,详述了实

- 关键字:

LVDS ADC数据接收信号 完整性FPGA

mini-lvds介绍

您好,目前还没有人创建词条mini-lvds!

欢迎您创建该词条,阐述对mini-lvds的理解,并与今后在此搜索mini-lvds的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473