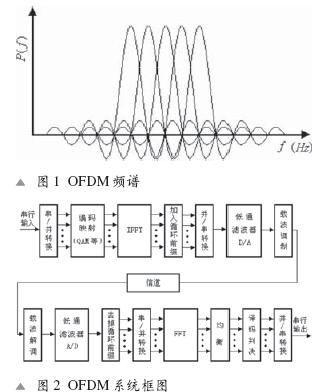

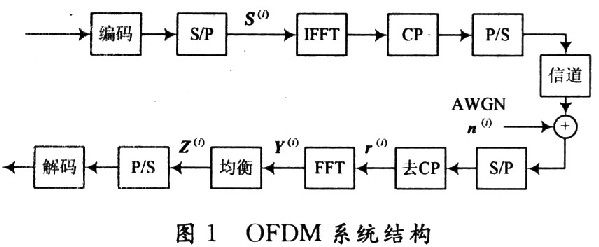

OFDM(正交频分复用)是一种高效的多载波调制技术,其最大的特点是传输速率高,具有很强的抗码间干扰和信道选择性衰落能力。OFDM最初用于高速MODEM、数字移动通信和无线调频信道上的宽带数据传输,随着IEEE802.11a协议、BRAN(Broadband Radio Access Network)和多媒体的发展,数字音频广播(DAB)、地面数字视频广播((DVB-T)和高清晰度电视((HDTV)都应用了OFDM技术。

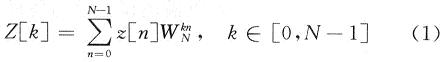

OFDM利用离散傅立叶反变换/离散傅立叶变换(IDFT/DFT)代替多载波调

关键字:

OFDM FPGA

O 引 言

随着各种FFT算法的出现,DFT在现代信号处理中起着越来越重要的作用。在B3G和4G移动通信中所采用的0FDM技术,更是以IDFT/DFT来进行OFDM调制和解调制,IDFT/DFT的精度直接影响基带解调的性能。

在硬件实现中,通常影响定点化FFT算法精度的有量化误差、舍入误差和溢出误差。一旦决定了量化方式和数据位宽后,量化误差和舍入误差都是可估计的,而溢出误差则随着输入信号功率的增大而急剧增加,造成SNR严重恶化。

中射频接收时,通常使用AAGc和DAGC来改善ADC正

关键字:

OFDM FPGA

O 引言

正交频分复用(OFDM)是一种正交多载波调制技术,它将宽带频率选择性衰落信道转换成一系列窄带平坦衰落信道,在克服信道多径衰落所引起的码间干扰,实现高数据传输等方面具有独特的优势。但是由于OFDM信号频谱重叠,对信道变化很敏感,在高速移动下,信道的时变特性更加明显,此时OFDM系统载波间的正交性会遭到破坏,出现载波间干扰(ICI),这会导致系统性能明显降低。为了消除ICI,必须采用适当的均衡技术以补偿ICI。国内外许多学者对这些问题进行了大量的研究,提出了各种不同的方法,得到了一些阶段性

关键字:

OFDM FPGA

一、 引言

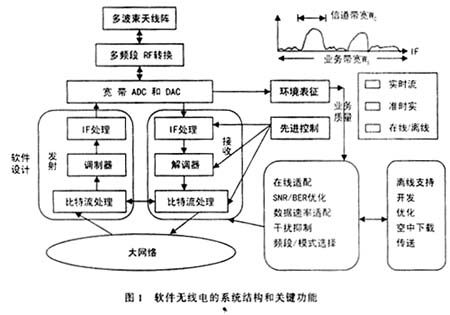

现代通信技术、微电子技术和计算机技术的飞速发展,促进了无线通信技术从数字化走向软件化。软件无线电的出现掀起了无线通信技术的又一次革命,它已经成为目前通信领域中最为重要的研究方向之一。所谓软件无线电,是指构造一个通用的、可重复编程的硬件平台,使其工作频段、调制解调方式、业务种类、数据速率与格式、控制协议等都可以进行重构和控制,选用不同的软件模块就可以实现不同类型和功能的无线电台,其核心思想是在尽可能靠近天线的地方使用宽带A/D和D/A变换器,并尽可能地用软件来定义无线功能[1]。

关键字:

FPGA 无线电

软件无线电的出现,是无线电通信从模拟到数字、从固定到移动后,由硬件到软件的第三次变革。简单地说,软件无线电就是一种基于通用硬件平台,并通 过软件可提供多种服务的、适应多种标准的、多频带多模式的、可重构可编程的无线电系统。软件无线电的关键思想是,将AD(DA)尽可能靠近天线和用软件来 完成尽可能多的无线电功能。

蜂窝移动通信系统已经发展到第三代,3G系统进入商业运行一方面需要解决不同标准的系统间的兼容性;另一方 面要求系统具有高度的灵活性和扩展升级能力,软件无线电技术无疑是最好的解决方案。用ASI

关键字:

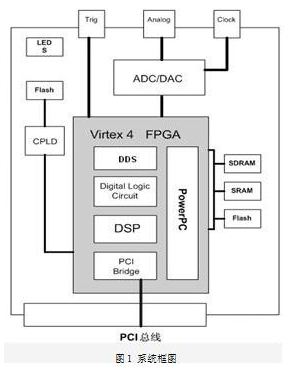

FPGA Virtex-4 PowerPC

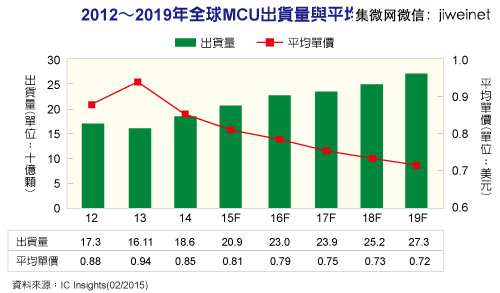

微控制器(MCU)需求持续走扬。市调机构IC Insights指出,在穿戴式与物联网等新兴嵌入式系统兴起的带动下,全球MCU出货量在2014年创下新高,达一百八十六亿颗,较2013年增长 16%,并超越2012年一百七十三亿颗的纪录;预估2015年将再成长12%,突破二百亿颗大关,2019年更可望达到二百七十三亿颗。

关键字:

物联网 MCU

全球最大微控制器厂商瑞萨电子5日于日股盘后发布新闻稿宣布,因日圆走贬、出售中小尺寸液晶面板用驱动IC研发/销售子公司“Renesas SP Drivers(以下简称RSP)”提列相关获利,加上固定成本删减措施奏功,故预估今年度(2014年4月-2015年3月)合并纯益将达740亿日圆(上年度为净损52亿日圆),将为史上(2010年由NEC电子、瑞萨科技合并以来)首度摆脱亏损局面;合并营益预估将大增44.9%至980亿日圆,合并营收预估将年减5.6%至7,860亿日圆、其中半导体

关键字:

瑞萨 MCU

一、什么是对立统一

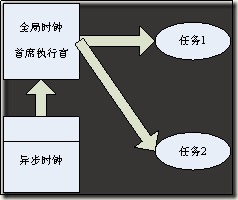

什么是CEO,就是首席执行官,是在一个企业中负责日常经营管理的最高级管理人员,又称作行政总裁,或最高执行长或大班。

那么,在FPGA系统,需不需要一个最高级别的执行官,来管理所有进程呢?为了系统的有序性,不至于凌乱、崩溃,答案必然是肯定的。

谁都知道,FPGA内部时序逻辑的工作,是通过时钟的配合来完成任务的。那么当系统中有异步时钟的时候,怎么办?每一个系统必须有一个最高级别的时钟,执行力最强;同时它担任着管理异步时钟的任务,其它异步时钟想让手下执行任务,必须告诉执

关键字:

FPGA 异步时钟

这个实验其实已经做好久了,但是一直没有做笔记,今天就把这部分的内容补一下,有兴趣的朋友可以看一下,或许对你有什么帮助,对初学者来说还是一个不错的实验。

先来了解一下VGA吧

我们家里用的台式电脑就是一个VGA显示器,小墨同学为做这方面的实验还特意买了一块7寸的VGA液晶显示器

记得当初自己也是傻得不得了,把写好的代码,烧到板子里就直接连到笔记本电脑上的VGA接口上,结果什么反应也没有,还调了一下午的程序...结果还是没反应,到群里一问才知道,原来笔记本电脑

关键字:

FPGA VGA

在逻辑设计领域,只涉及单个时钟域的设计并不多。尤其对于一些复杂的应用,FPGA往往需要和多个时钟域的信号进行通信。异步时钟域所涉及的两个时钟之间可能存在相位差,也可能没有任何频率关系,即通常所说的不同频不同相。

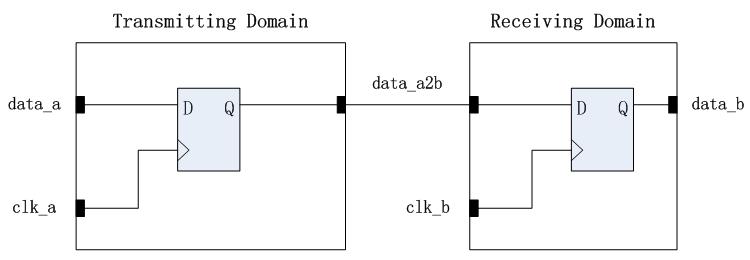

图1是一个跨时钟域的异步通信实例,发送域和接收域的时钟分别是clk_a和clk_b。这两个时钟频率不同,并且存在一定的相位差。对于接收时钟域而言,来自发送时钟域的信号data_a2b有可能在任何时刻变化。

图1 跨时钟域通信

对于上述的异步时钟域通

关键字:

FPGA 信号处理

摘要

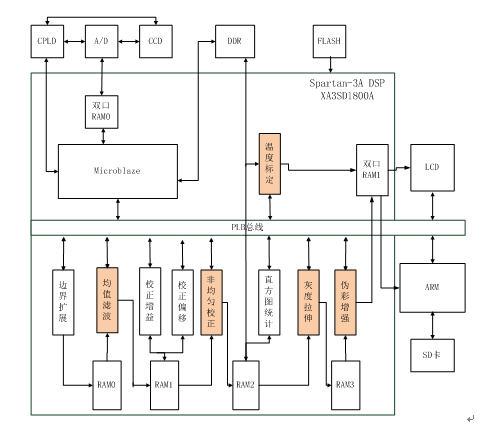

人类接收的信息约有70%来自视觉。因此,图像采集及处理设备在人们的日常生活中占有很重要的地位。随着互联网的普及及带宽的提高,使得图像的网络传输成为可能,且应用范围越来越广,为人们的日常生活带来了极大的便利。同时,随着非制冷红外技术的发展,红外热像系统在军用和民用领域得到了广泛的应用。根据美国红外市场权威调查机构Maxtech International发布的2006年度红外市场报告,2003年至2006年全球民用红外热像仪的平均增长幅度为17%,并且正展现出更广阔的市场需求。

由此可

关键字:

FPGA ARM Microblaze

项目背景

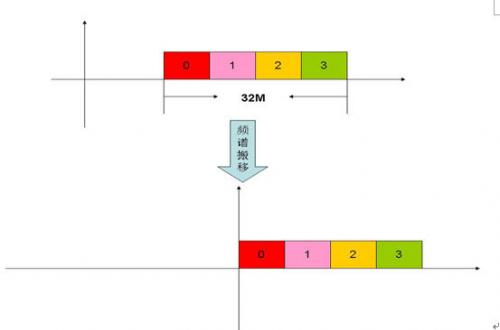

项目名称:认知无线电的频谱检测

项目背景:随着无线通信需求的不断增长,可用的频谱资源越来越少,呈现日趋紧张的状况;另一方面,人们发现全球授权频段尤其是信号传播特性较好的低频段的频谱利用率极低。认知无线电技术为解决频谱利用率低的问题提供了行之有效的方法。由于认知无线电在使用空闲频段进行通信的同时不断地检测授权用户的出现,一旦检测到授权用户要使用该频段,认知无线电用户便自动退出并转移到其他空闲频段继续通信,确保在不干扰授权用户的情况下,与他们进行频谱共享。这样一来,在没有增加新频段的

关键字:

FPGA 无线电

本文介绍Virtex - 5 FXT FPGA系列浮点接口,赛灵思logiCORE的IP处理器单元( APU )辅助PowerPC 440嵌入式微处理器设计的IP基础知识。

点击此处下载

关键字:

Virtex-5 FPGA

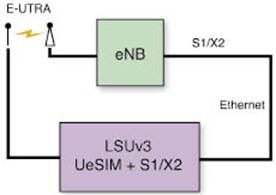

功能强大的可编程逻辑平台使得Prisma Engineering公司能够针对所有蜂窝网络提供可重配置无线测试设备。长期演进(LTE)是移动宽带的最3GPP标准,它打破了现有蜂窝网络的固有模式。LTE与前代UMTS和GSM标准相比,除采用高频谱效率的射频技术外,其架构还得到了大幅简化。LTE系统的无线接入部分Node-B,是连接无线电和整个互联网协议核心网络之间的边缘设备。这种架构无法监测和测试等效于UMTS中间链路上的元件。必须通过无线电接口,才能有效地测试LTE网络元件。

这正是Prisma

关键字:

Virtex-5 FPGA 仿真器

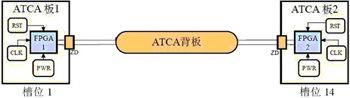

1 引言

随着电子系统的不断发展,芯片间以及板间的数据传输需求也在不断增长,传统的单端并行数据传输模式早已不能满足现在高带宽应用的要求。USB 3.0、SATA 3.0、PCI-E 2.0等新串行规范的发布以及更高速的串并/并串转换单元(SERDES)芯片的推出更是引起了业界对高速差分串行数据传输的无限憧憬。为了解决下一代无线通信基站中多天线(MIMO)信号处理所带来的巨大数据吞吐量要求,本文基于Virtex-5 FPGA的GTP单元给出了一种在高级电信计算架构(ATCA)机箱内实现单对差分线进

关键字:

FPGA Virtex-5

mcu-fpga介绍

您好,目前还没有人创建词条mcu-fpga!

欢迎您创建该词条,阐述对mcu-fpga的理解,并与今后在此搜索mcu-fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473