- 设计了一组基于CPLD的PLC背板总线协议接口芯片,协议芯片可以区分PLC的背板总线的周期性数据和非周期性数据。详细介绍了通过Verilog HDL语言设计状态机、协议帧控制器、FIFO控制器的过程,25MHz下背板总线工作稳定的试验结果验证了协议芯片设计的可行性。

- 关键字:

VerilogHDL PLC背板 CPLD

- 基于数字信号处理器(DSP)TMS320VC5416和复杂可编程逻辑器件(CPLD)的嵌入式车牌识别系统的硬件设计,利用视频处理芯片SAA7111作为视频A/D,在CPLD的控制下将采集到的图像数据写入帧存储器中,DSP对图像数据进行实时分析处理。采用“乒乓”存储结构,实现了图像数据的采集和处理的并行运行。识别结果通过串口传到上位机或者保存在E2PROM中,实现了车牌识别系统脱机、联机工作,在实时高速图像处理系统中有广泛的工程技术应用前景。

- 关键字:

车牌识别系统 嵌入式 CPLD

- 以CPLD作为主控芯片,设计了一种针对USB总线的数据读写控制器。u盘通过该控制器转接到Pc机的USB接口,利用控制器对usB总线上的数据进行实时监测分析,自动禁止Pc机上的文件数据输出到U盘,同时不影响Pc机对u盘中文件的正常读取。

- 关键字:

USB接口 读写控制器 CPLD

- 本项目使用Virtex-5 OpenSPARC评估平台,首先通过VGA解码芯片,将PC机中的视频流数据解码出R、G、B信号值和场、行信号。然后使用OV7670数字摄像头,摄取人体的手部动作,运用一定的算法,对摄像头数据进行处理,判定此时的人体动作,然后将其与RGB分量信号进行叠加,通过配置DVI接口芯片,将叠加后的图像送至显示器显示。

- 关键字:

Virtex-5 动作识别 DIY 数字摄像头 FPGA

- 可编程逻辑器件的D触发器资源非常有限,而且可编程逻辑器件在控制时序方面不如单片机那样方便,很多不熟悉的应用者往往感到应用起来非常的困难。利用可编程逻辑器件和单片机构成的双向通信控制器克服了两者的缺点,且把二者的长处最大限度地发挥出来。

- 关键字:

可编程逻辑器件 双控制器 AT89C51 CPLD 单片机

- 数据采集系统是通过采样电路将输入的模拟信号转换成离散信号,并送入CPU、MCU或DSP进行处理。现在流行的基于PCI总线设计的采集卡是数据采集系统的主流,其优点是可以利用PCI总线的研究成果快速的开发系统软件,整体运行速度快,能够实现实时采集实时处理。但在一些工业测控现场检测大型设备时,从现场到机房有一定的距离,模拟信号传到安装在PC内的PCI数据采集卡会有不同程度的衰减,且易受工业环境的干扰。而单纯用由微控制器(MCU)为核心的数据采集系统时,把数据采集器置于被监测的设备处,虽然可以避免模拟信号的衰减和

- 关键字:

数据采集 ARM μC/OS-II CPLD

- 传统意义上,ASIC和CPLD是低功耗竞争中当仁不让的赢家。但是由于相对成本较高,且用户对高端性能和额外逻辑的要求也越来越多,在低功耗应用中使用CPLD正在失去优势。ASIC也面临相同的风险。而例如FPGA这样日益增长的可编程半导体器件正逐步成为备受青睐的解决方案。

- 关键字:

低功耗 ASIC CPLD 可编程半导体器件

- 0 引 言 本系统以AD7892SQ和CPLD(复杂可编程逻辑器件)为核心设计了一个多路信号采集电路,包括模拟多路复用、集成放大、A/D转换,CPLD控制等。采用硬件描述语言V

- 关键字:

EDA CPLD FPGA

- 同步时钟信号是分布式录波器系统任务顺利完成的关键。介绍一种利用可编程CPLD器件实现性能优良的分布式同步信号源。通过高度集成,将IRIG-B(DC)解码器以及系统的各种同步逻辑电路集成在一个MAXII570芯片中,构成一个高精度同步系统,从而达到最佳同步效果。

- 关键字:

分布式同步逻辑 IRIG-B CPLD

- 设计了一种全新构架的高性能数据采集系统。采用平衡式双通道对称结构,可对32路输入信号进行灵活控制。系统中采用了高速A/D转换器、大容量的FIFO SRAM、CPLD技术和PCI数据通信接口,实现了实时、高速的数据采集和处理。

- 关键字:

高速实时数据采集 平衡式双通道 CPLD

- LED点阵显示屏是集微电子技术、计算机技术、信息处理技术于一体的大型显示屏系统。它以其色彩鲜艳,动态范围广,亮度高,寿命长,工作稳定可靠等优点而成为众多显示媒体以及户外作业显示的理想选择。目前,已经被广泛应用到军事、车站、宾馆、体育、新闻、金融、证券、广告以及交通运输等许多行业。

- 关键字:

LED点阵 控制系统 发光管 FPGA CPLD

- 引言 现代电信系统已发展为一个庞大的综合化数字网络,除了提供传统电话服务外,也提供多种数据接入服务,其典型应用是为其它专用通信系统提供数据中继服务。因E1信号接入方式简单,一般电信交换机都会预留部分E1接入端口以供专用通信系统使用。为满足电信网接入要求并充分利用线路资源,E1终端子系统内部常采用ST-BUS总线对各路用户数据进行复接或解复接,并实现与E1信号的转换。考虑到专用接口芯片针对某一种或几种标准接口而设计,已无法满足所有接口标准(尤其是新型接口标准)要求。为使各种接口都能与电信线路进行数据交

- 关键字:

CPLD ST-BUS

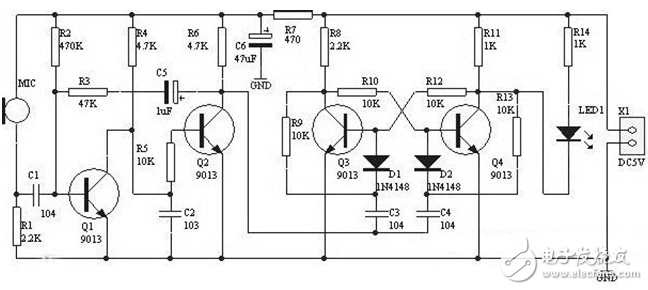

- 电路如附图所示(点击放大).通电时+5.5V电源通过R1对C1充电,同时也通过R2对C2充电,但由于R1、C1的时间常数很大.所以C2先充好电。由于555的第②脚的电压高于第⑥、⑦脚,它的第③脚便会输出低电平,致使Q1截止,Q2导通,继电器J...

- 关键字:

DIY 路由器 定时关机

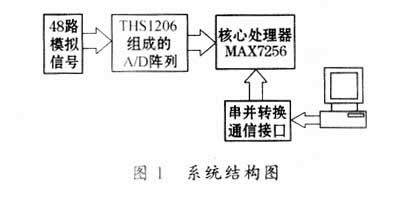

- 摘要 介绍了一种多通道应变信号采集系统的模块化设计,解决了飞机强度监测中应用大批量电阻式应变片数据采集和传输的问题。该设计采用3级模块级联而成,可同时采集4096路应变信号。利用CPLD实现对4096路模拟信号的数

- 关键字:

飞机强度 应变片 CPLD

cpld-diy介绍

您好,目前还没有人创建词条cpld-diy!

欢迎您创建该词条,阐述对cpld-diy的理解,并与今后在此搜索cpld-diy的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473