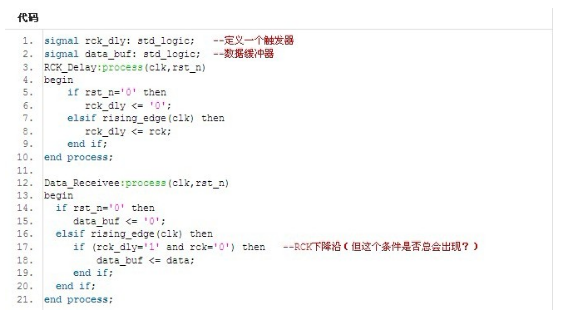

- 在同步电路设计中,边沿检测是必不可少的! 例如:在一个时钟频率16MHz的同步串行总线接收电路里,串行总线波特率为1Mbps。在串行总线的发送端是在同步时钟(1MHz)的上升沿输出数据,在接收端在同步时钟的下降沿对输入数据进行接收采样。在这个接收电路里检测同步时钟的下降沿是必不可少的。假设主时钟-clk,同步时钟-rck,同步数据-data。 有些人在边沿检测的时候就喜欢这样做:

但是大家忽略了一种情况,就是clk与rck之间比没有必然的同步关系,当r

- 关键字:

FPGA 边沿检测

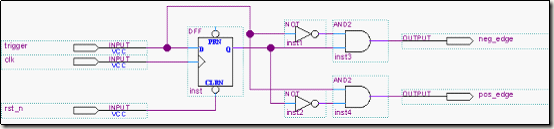

- 1、所谓边沿检测,就是检测输入信号或FPGA内部逻辑信号电平的跳变,即实现上升沿或下降沿的检测,捕获到以后以此用作使能信号(简单可理解为:一旦检测到这个信号,则发生什么什么),来作为时序逻辑的触发信号。总之,在基础中,这个还是很重要的,在后面的串口和SPI接口中都要用到。 (一)、一级寄存器

从一级寄存器中很好理解下降沿和上升沿的检测:a和b都是从trigger来的(三者一样),只是b比a在时间上迟了一个寄存器的时间。现在假设0时刻到了,trigger到

- 关键字:

边沿检测 寄存器

- 一、为什么要讲边沿检测

也许,没有那么一本教科书,会说到这个重要的思想;也许,学了很久的你,有可能不知道这个重要的思想吧。很惭愧,我也是在当年学了1年后才领悟到这个思想的。

说实话,我的成长很艰辛,没有人能给我系统的指导,而我得撑起这一片蓝天,于是乎无数个漏洞,我一直在修补我的不足。我没能对自己满足过,不是说我“贪得无厌”,而是,我不够“完美”。人可以不完美,但不可以不追求完美;或许终点永远达不到,但努力的过程,你一直在靠近完美;有方向感地奋

- 关键字:

FPGA 边沿检测

边沿检测介绍

您好,目前还没有人创建词条边沿检测!

欢迎您创建该词条,阐述对边沿检测的理解,并与今后在此搜索边沿检测的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473