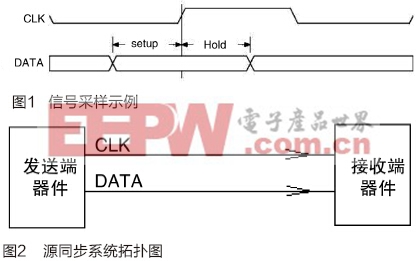

- 摘要:本文针对高速电路设计中经常面临的时序问题,提出了时序分析和计算方法,并结合SPI4.2接口给出了具体分析实例。

1 满足接收端芯片的建立/保持时间的必要性

在高速数字电路设计中,由于趋肤效应、临近干扰、电流高速变化等因素,设计者不能单纯地从数字电路的角度来审查自己的产品,而要把信号看作不稳定的模拟信号。采用频谱分析仪对信号分析,可以发现,信号的高频谱线主要来自于信号的变化沿而不是信号频率。例如一个1MHz的信号,虽然时钟周期为1微秒,但是如果其变化沿上升或下降时间为纳秒级,则在频谱仪

- 关键字:

DATA 源同步系统 数据类信号 时序 TSCLK 201412

数据类信号介绍

您好,目前还没有人创建词条数据类信号!

欢迎您创建该词条,阐述对数据类信号的理解,并与今后在此搜索数据类信号的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473