● 此次收购将帮助系统级芯片 (SoC) 设计人员通过经市场检验的时序约束管理能力来加速设计,并提高功能约束和结构约束的正确性西门子宣布收购Excellicon公司,将该公司用于开发、验证及管理时序约束的软件纳入西门子EDA的产品组合。此次收购将帮助西门子提供实施和验证流程领域的创新方法,使系统级芯片 (SoC) 设计人员能够优化功耗、性能和面积 (PPA),加快设计速度,增强功能约束和结构约束的正确性,提高生产效率,弥合当前工作流

关键字:

西门子 Excellicon EDA 时序约束

从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下: 1. 核心频率约束 这是最基本的,所以标号为0。 2. 核心频率约束+时序例外约束 时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 3. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时(Inpu

关键字:

FPGA 时序约束

从最近一段时间工作和学习的成果中,我总结了如下几种进行时序约束的方法。按照从易到难的顺序排列如下: 1. 核心频率约束 这是最基本的,所以标号为0。 2. 核心频率约束+时序例外约束 时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序约束。如果仅有这些约束的话,说明设计者的思路还局限在FPGA芯片内部。 3. 核心频率约束+时序例外约束+I/O约束 I/O约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时(Inpu

关键字:

FPGA 时序约束

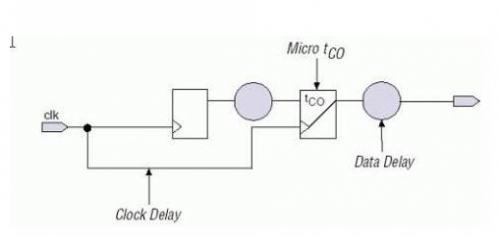

时钟上升沿和下降沿之间的时序约束

周期约束可以自动计算两个沿的的约束——包括调整非50%占空比的时钟。

例:一个CLK时钟周期约束为10ns,能够应用5ns的约束到两个寄存器之间。

不需要特定路径应用到这个例子中。

相关时钟域的约束

为一个时钟进行周期约束——以这个周期约束确定相关的时钟。

执行工具将根据它们的关系来决定如何处理跨时钟域。

DCM有多个输出:

—&md

关键字:

ISE 时序约束

回顾全局OFFSET约束

在时钟行中使用Pad-to-Setup和Clock-to-Pad列为所有出于该时钟域的I/O路径指定OFFSETs。

为大多数I/O路径进行约束的最简单方法——然而,这将会导致一个过约束的设计。

指定管脚的OFFSET约束

使用Pad-to-Setup和Clock-to-Pad列为每个I/O路径指定OFFSETs。

这种约束方法适用于只有少数管脚需要不同的时序约束。

更常用的方法是:

1. 为Pads生成Gro

关键字:

ISE 时序约束

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

下文总结了几种进行时序约束的方法。按照从易到难的顺序排列如下:

0. 核心频率约束

这是最基本的,所以标号为0。

1. 核心频率约束+时序例外约束

时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay。但这还不是最完整的时序

关键字:

FPGA 时序约束

特定路径时序约束

使用全局时序约束(PERIOD,OFFSET,PAD-TO-PDA)将约束整个设计

仅仅使用全局约束通常会导致过约束

——约束过紧

——编译时间延长并且可能阻止实现时序目标

——通过综合工具或者映射后时序报告重新审视性能评估

特定路径约束能够覆盖全局时序约束在特定路径上的约束

——这就允许设计者放宽特定路径的时序要求

更多关于特定路径约束

关键字:

ISE 时序约束

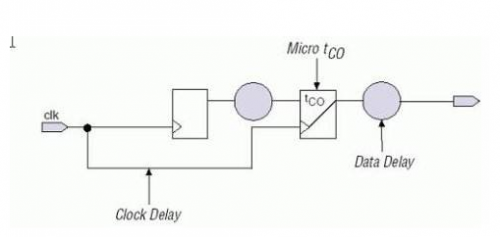

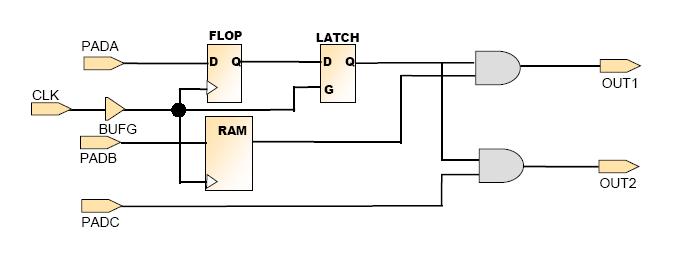

问题思考

在这个电路中哪些路径是由OFFSET IN 和 OFFSET OUT来约束的?

问题解答:

——OFFSET IN:PADA to FLOP and PADB to RAM

——OFFSET OUT:LATCH to OUT1, LATCH to OUT2, and RAM to OUT1

问题思考

下面给出的系统框图里,你将给出什么样的约束值以使系统能够跑到100MHz?

关键字:

ISE 时序约束

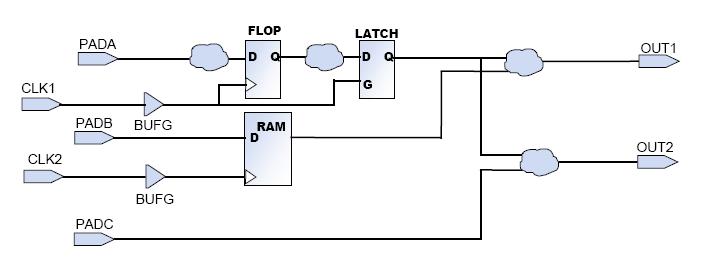

问题思考

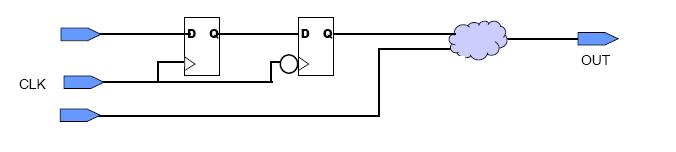

哪些路径是由CLK1进行周期约束?

哪些路径是由pad-to-pad进行约束?

OFFSET约束

OFFSET约束覆盖以下路径:

——从input pads到同步单元(OFFSET IN)

——从同步单元到output pads(OFFSET OUT)

OFFSET约束特性

OFFSET约束自动计算时钟分布延时

1. 提供最准确的时序信

关键字:

ISE 时序约束

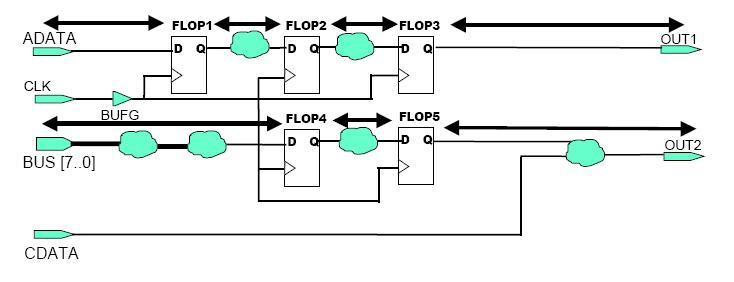

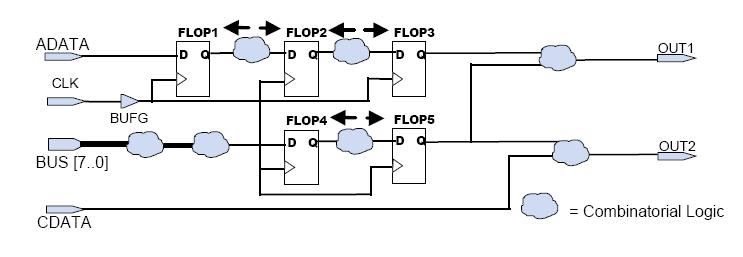

问题思考

单一的全局约束可以覆盖多延时路径

如果箭头是待约束路径,那么什么是路径终点呢?

所有的寄存器是否有一些共同点呢?

问题解答

什么是路径终点呢?

——FLOP1,FLOP2,FLOP3,FLOP4,FLOP5。

所有的寄存器是否有一些共同点呢?

——它们共享一个时钟信号,约束这个网络的时序可以同时覆盖约束这些相关寄存器间的延时路径。

周期约束

周期约束覆盖由参

关键字:

ISE 时序约束

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

下文总结了几种进行时序约束的方法。按照从易到难的顺序排列如下:

0.核心频率约束

这是最基本的,所以标号为0.

1.核心频率约束+时序例外约束

时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay.但这还不是最完整的时序约束

关键字:

FPGA 时序约束

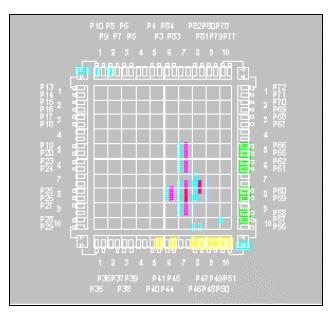

时序约束和你的工程

执行工具不会试图寻找达到最快速的布局&布线路径。——取而代之的是,执行工具会努力达到你所期望的性能要求。

性能要求和时序约束相关——时许约束通过将逻辑元件放置的更近一些以缩短布线资源从而改善设计性能。

没有时序约束的例子

该工程没有时序约束和管脚分配

——注意它的管脚和放置

——该设计的系统时钟频率能够跑到50M

关键字:

ISE 时序约束

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执行约束的效果越了解,那么对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更可控。

下文总结了几种进行时序约束的方法。按照从易到难的顺序排列如下:

0.核心频率约束

这是最基本的,所以标号为0.

1.核心频率约束+时序例外约束

时序例外约束包括FalsePath、MulticyclePath、MaxDelay、MinDelay.但这还不是最完整的时序约束

关键字:

FPGA 时序约束

对自己的设计的实现方式越了解,对自己的设计的时序要求越了解,对目标器件的资源分布和结构越了解,对EDA工具执 ...

关键字:

时序约束 EDA工具 核心频率

时序约束介绍

您好,目前还没有人创建词条时序约束!

欢迎您创建该词条,阐述对时序约束的理解,并与今后在此搜索时序约束的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473