- 摘要:HDB3(三阶高密度双极性)码具有无直流分量、低频成分少、连零个数不超过3个、便于提取时钟信号等特点。通过对HDB3编解码原理进行分析和研究,提出一种基于FPGA的HDB3编解码实现方法,给出Verilog HDL语言的实现

- 关键字:

FPGA HDB3 编解码

- 日前,德州仪器 (TI) 在英国伯明翰举行的全球规模最大的年度安全技术大会——国际安全与消防展览会(IFSEC)上演示了具有 D1 分辨率(720 x 480 逐行扫描,速度为每秒 30 帧)的单处理器 8 通道 H.264 主类编码解决方案。当前设计解决方案需要两个以上处理器才能实现该单处理器所提供的这一性能,因此开发人员可精简 BOM 成本。这将显著降低单位 D1 通道成本,而且开发人员可充分利用复杂性更低的硬件设计方案创建数码摄像机(DVR)、数字视频服务器(DVS)等更

- 关键字:

TI 编解码 处理器

- 高压缩比标准的各种特性为技术人员提供了广阔的空间,在复杂性、延迟以及其他约束实时性能的因素之间获得最佳...

- 关键字:

视频 编解码 多媒体

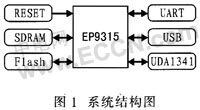

- 1 引言

近几年,MP3音频产品受到消费者的青睐,而高质量的音效是当前MP3音频产品发展的重要趋势。MP3文件解码一般采用软件解码和硬件解码两种方法。硬件解码实现简单,但需增加硬件成本。软件解码需占用大量CPU时间,实现难度大,但成本低、处理灵活,只要CPU具有足够的处理速度则是一种很好选择。本文介绍了MP3文件播放系统硬件和软件设计,采用Cirrus Logic公司的EP9315处理器和UDA1341编解码器,并介绍了基于μC/OS-II开源实时操作系统的MP3解码原理,播放函数以及硬件

- 关键字:

MP3 编解码 CPU μC/OS-II

- 随着数字多媒体的应用日渐广泛,视频解码在嵌入式系统设计中变成一个基本要素。视频标准有多种,依赖于产品可实施其中的一个或者多个标准。

当然这不是全部,视频仅仅是多媒体码流的一部分,另外还有音频或者语音需要并行处理。因此,一个精确的处理存储或数据流的同步层是必需的。此外,视频解码本身对性能要求较高,需要不同于先前基于语音和信息应用的系统架构;这就对便携系统提出了特殊挑战,而桌面应用同样面临这些问题。

&n

- 关键字:

嵌入式 DSP 视频 编解码

- 不只在高解析视讯应用上发光发热,H.264针对中低分辨率,也能发挥其降低流量的长处,因此应用于网络实时串流传输,或者是移动装置上小屏幕视讯的播放,都是非常合宜的方式。 由H.264具有一系列优于MPEG4和H.263的特性,在相同的重建图像质量下,能比H.263节省约50%左右的流量。但是,在获得优越性能的同时,H.264的计算复杂度却大大

- 关键字:

H.264 编解码 通信 嵌入式系统 DSP 多媒体 消费类电子 嵌入式 消费电子

- 摘 要:本文简要介绍了基于IXP421的语音网关的系统结构,以及语音DSP模块的工作原理。系统中没有专用的语音DSP,而是由IXP421的XSCALE核实现。系统软件、应用软件和语音DSP共享CPU时间。语音处理能力会受到编码方式和CPU负荷的制约,因此,本文通过实际系统的测试结果对Intel公司声明的性能指标进行了验证。关键词:VoIP;DSP;XSCALE;编解码

引言就VoIP设备来说,如果语音处理器的功能和其它应用功能由一个处理器来完成,必然能极大地简化电路,降低成本。Intel的I

- 关键字:

DSP VoIP XSCALE 编解码 通讯 网络 无线

- 介绍了HDB3编解码的原理和方法,给出了用CPLD实现E1信号HDB3编解码的方法,同时给出了它的实现原理图,最后给出了XILINX的XC9500系列可编程逻辑器件的开发流程。

- 关键字:

9572 HDB3 XC 编解码

编解码介绍

您好,目前还没有人创建词条编解码!

欢迎您创建该词条,阐述对编解码的理解,并与今后在此搜索编解码的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473