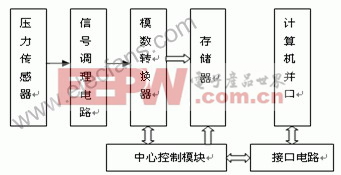

- 在爆炸场压力测试中,冲击波超压峰值随着弹药的当量和到爆心距离的变化十分显著。传统测试系统的测试参数难以更改,灵活性差,往往需要重新设计电路以满足不同测试要求。为了提高测试系统的灵活性及电路复用性,设计了基于可配置FPGA软核的测试系统。通过调用并修改可移植软核,以实现系统的快速设计,通过灵活设置测试参数完成不同测试任务。对系统准确性进行了验证,应用到静爆试验中,有效获得了压力数据。

- 关键字:

FPGA 软核 冲击波 存储测试

- 采用CPLD的水下冲击波记录仪的应用设计,1.引言

随着大规模集成电路和单片机的迅速发展,复杂可编程逻辑器件(CPLD)具有使用灵活、可靠性高、功能强大的优点,在电子产品设计中得到了广泛的应用。CPLD可实现在系统编程,重复多次,而且还兼容IEEE1

- 关键字:

应用 设计 记录仪 冲击波 CPLD 水下 采用

- 基于CPLD的水下冲击波记录仪的设计,1.引言

随着大规模集成电路和单片机的迅速发展,复杂可编程逻辑器件(CPLD)具有使用灵活、可靠性高、功能强大的优点,在电子产品设计中得到了广泛的应用。CPLD可实现在系统编程,重复多次,而且还兼容IEEE1

- 关键字:

记录仪 设计 冲击波 水下 CPLD 基于

- 1.引言

随着大规模集成电路和单片机的迅速发展,复杂可编程逻辑器件(CPLD)具有使用灵活、可靠性高、功能强大的优点,在电子产品设计中得到了广泛的应用。CPLD可实现在系统编程,重复多次,而且还兼容IEEE1149.1(JTAG)标准的测试激励端和边界扫描能力,使用CPLD器件进行开发,不仅可以提高系统的集成化程度、可靠性和可扩充性,而且大大缩短产品的设计周期。由于CPLD采用连续连接结构,易于预测延时,从而使电路仿真更加准确。CPLD是标准的大规模集成电路产品,可用于各种数字逻辑系统

- 关键字:

CPLD 测量 测试 冲击波 记录仪

冲击波介绍

您好,目前还没有人创建词条冲击波!

欢迎您创建该词条,阐述对冲击波的理解,并与今后在此搜索冲击波的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473