基于PSoC的防高压电容测量设计与实现(08-100)

根据上面所述的充电法电容参数测量特点,如果需要设计一款只测电容容量参数,而且能防高压的电容测试系统,那么问题的关键就集中到一点:具有一个大范围,高精准,可编程的恒流源。事实上,我们在上面介绍PSoC时已经提到了,PSoC都具有可实现充电法测量电路所需的比较器,计数器之外的可编程模拟和数字模块之外,还具有可编程恒流源(IDAC)硬件资源。因此,基于PSoC来实现一个耐高压,宽量程,高精度,低成本的电容容量测试系统会是一件很容易做到的事情。

本文引用地址:http://www.eepw.com.cn/article/91854.htm基于PSoC的防高压电容容量测量方案实现

根据我们上面对基于PSoC的防高压电容容量测量方案的可行性,实现拓朴以及PSoC 内部架构的阐述,我们可以知道要实现这一方案需要做如下几部分设计:防高压测量外围电路设计,PSoC模块配置设计和测量软件设计。下面我们将对其分别进行介绍。

防高压电容测量外围电路设计

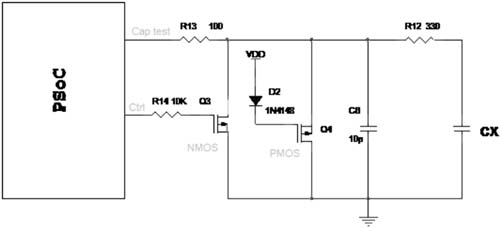

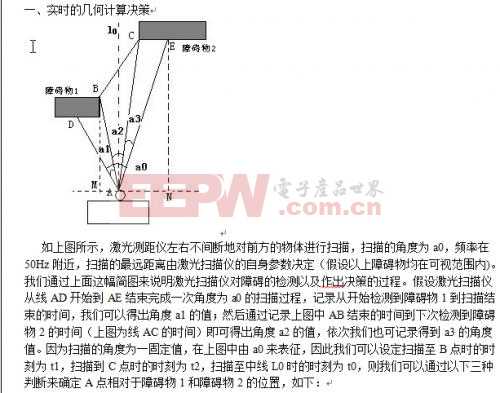

图3 电容测量外围电路

图3是基于PSoC进行电容测量的外围电路,充电测量时,PSoC内的IDAC(可编程恒流源)通过Cap test引脚输出恒定电流经过R13,R12分别对待测电容CX和已知电容容量C8充电,Cap test引脚上的电压就会线性增高,一旦达到参考电压Vref时,PSoC内部的比较器就会翻转产生控制信号给PSoC内的微控制器,微控制器就会将计数结果取走进行容值计算与显示,从而容值测量;同时比较器翻转中断信号也会触发放电控制引脚Ctrl置高,将NMOS管导通,为CX,C8提供放电电路。在此还有一个PMOS管未提及的作用。这个PMOS管就是用来专门为了防高压而设计的。当带高压电荷(比VDD电源高的电压电荷)的待测电容CX放到测试夹具进行测试时,PMOS管的源极S电压就变为待测电容上的电压值,由于PMOS管的栅极电压近似为VDD,因此PMOS管就会瞬间导通,一直导通到CX上的电压 低于VDD,PMOS管才会关闭。所以PMOS管构成了高压硬件放电通路,从而确保PSoC不会受到高压电荷长时间的冲击。图中电阻R12为330Ω,PMOS管的工作电流为1A,因此,采用该电路可耐1A×330Ω=330V的高压电荷。330V的耐压指标对普通的电子工程师来讲一般是足够了,因为常用的电子电器产品的交流电为220V。当然如果还需要耐更高的电压信号,可以将R12电阻加大或选择导通电流更大的PMOS管。

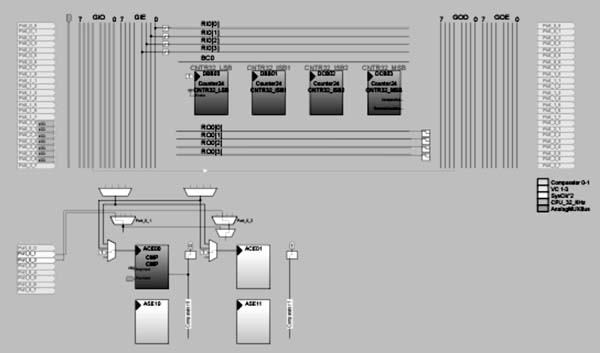

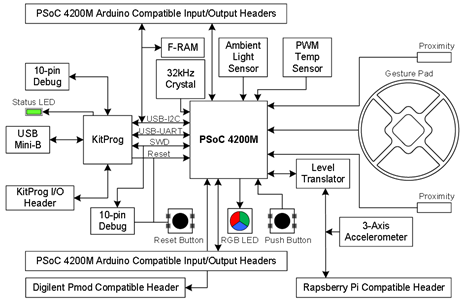

PSoC模块配置设计

图4 PSoC内部模块配置图

评论