65nmCyclone III FPGA可降低50%的功耗

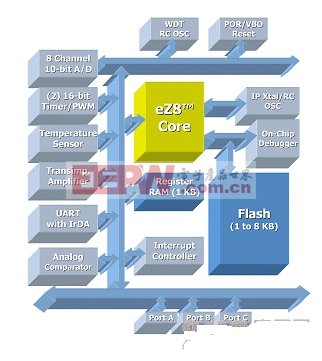

“与前一代90nm工艺器件相比,65nm Cyclone III系列可节省50%的功耗。”Altera公司广播、汽车电子及消费电子业务部副总裁Tim Colleran强调,“此外,Cyclone III的密度加倍,达到120K逻辑单元(LE);存储器容量高达4Mb;乘法器数量由150个增长到288个;由于它采用M9K存储器模块取代M4K模块,因此更适合视频流缓冲和视频图像处理。”Cyclone III FPGA系列由8个型号组成,容量分布在5K至120K逻辑单元之间。由于前一系列的Cyclone II系列已经比竞争产品的速率高出3个等级,Altera选择对Cyclone III系列的功耗、性能和成本进行改进,提高了嵌入式乘法器、板上存储器和外部存储器接口以及I/O的性能,而保持内核逻辑的性能与Cyclone II系列一致。

利用TSMC的65nm低功耗(LP)工艺技术以及Quartus II软件独特的功耗管理等多种技术,Cyclone III系列的功耗比Cyclone II系列降低了50%,更比竞争FPGA的功耗低75%。TSMC的65nm LP工艺针对便携式和消费类市场(例如DVR、手持式设备和便携式媒体播放器等领域)进行了精确调整,具有最低的静态功耗和动态功耗。在25℃结温时,内核静态功耗低至35mW。支持热拔插操作,因此在零电流时可以关断不工作的I/O块。此外,Quartus II开发软件的PowerPlay技术对设计进行自动分析和优化、降低功耗,同时满足时序和性能要求。低功耗优势包括能够在散热困难的环境中工作、降低甚至避免了在制冷系统上的投入、延长了便携式应用中电池的使用时间。

|

| Cyclone III FPGA的平面布局。 |

在成本方面,Cyclone III系列比前一代产品每逻辑单元成本降低20%,使设计人员能够更多地在成本敏感的应用中使用FPGA。Cyclone III采用交错I/O焊环来减小管芯尺寸和电路板面积,多种低成本封装选择以及低成本并行闪存配置器件使其成为成本极低的FPGA解决方案。

除了汽车行业和消费电子等对成本较为敏感的应用将采用Cyclone III系列等低成本FPGA,无线市场也是Cyclone III系列的重点发展领域,应用范围包括无线基站、软件无线电和显示,以及图像和视频处理等。“Cyclone III FPGA适合任何需要采用FPGA的设计,但是基于该器件在功耗和成本上的优势,特别适合于显示、无线和视频图像处理等应用。”Tim Colleran指出。

Cyclone III FPGA的其它优点包括:更多的I/O特性支持(包括针对显示应用的LVDS、mini LVDS、RSDS和PPDS);支持高达400Mbps的DDR2存储器接口;全功能PLL(提高了频率范围,可动态改变频率和相位,并能够级联产生更宽的频率范围)等。

Altera已为客户提供了全面的开发工具Quartus II软件7.0。设计人员现在可以下载并安装免费的Quartus II网络版软件7.0来开始Cyclone III设计。在这个新版Quartus II软件中,Altera提供了开发成本最低、时间最短的设计过程,从而确保了设计流程的流畅。Quartus II软件还与所有主流第三方综合以及仿真工具实现了无缝集成。

利用Quartus II软件的高级技术和效能特性,设计人员能够充分挖掘Cyclone III系列的潜能。Quartus II软件7.0的特性包括:TimeQuest时序分析器,快速方便地实现时序逼近。渐进式编译缩短了编译时间,支持基于团队的设计。PowerPlay功耗分析和优化工具进行低功耗估算,SoPC Builder和DSP Builder工具进行系统级设计。更新后的SDC时序约束功能支持Cyclone III器件迅速实现高速源同步接口(例如,DDR和DDRII)和时钟复用设计结构的时序逼近。

评论