两种基于FPGA的软件滤波方法

1. 3延时滤波程序仿真

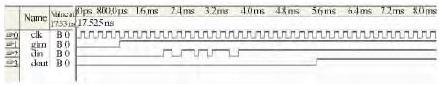

本文引用地址:http://www.eepw.com.cn/article/278137.htm分别将开关信号din设置成理想信号和抖动信号,利用QuartusⅡ8. 0软件进行仿真,图3和图4分别为理想信号和抖动信号的延时滤波仿真波形图。

图3理想开关信号延时滤波仿真波形

图4抖动开关信号延时滤波仿真波形

图中clk为采样时钟,glrn为复位信号,din为开关输入信号,dout为延时滤波输出信号。从图3可以看出,从开关信号发生变化到输出发生变化的时间延时为2 ms,从图4中可以看出,此延时滤波程序有效消除了扭子开关的抖动干扰,验证了其理论可行性。

1. 4延时滤波程序实际验证

为了验证此延时滤波程序的实际滤波效果,将其下载到Xilinx公司的Spartan3系列FPGA芯片XC3S400中,用示波器多次测量经过滤波后的开关信号,得到图5所示的输出信号波形。图5中,横坐标表示时间,每格代表10μs,纵坐标表示电压,每格表示1 V.从图5可以看出,经过滤波后的开关信号不再有抖动现象,此延时滤波程序的实际可靠性得到验证。

图5延时滤波后的输出信号波形

1. 5延时滤波程序资源占用率

在电子电路的设计中,FPGA的资源占用率是我们应该考虑的一个重要问题。如果FPGA的资源占用率太大,会加重FPGA的负担,影响整个电路的运行速度。表1为延时滤波程序在XC3S400芯片中的资源占用情况。

表1延时滤波程序的资源占用情况

1. 6延时滤波的特点

延时滤波比较适合对脉冲宽度已知的干扰信号进行滤波,这样可以更准确地确定延时时间,既不会因为延时时间太短而导致滤波不理想,又不会因为延时时间过长而导致资源浪费。而且,延时程序不仅可以有效地消除开关类信号的抖动,还可以滤去干扰、噪音等其他尖峰波,抗干扰强,可靠性高。

如果电路中存在多路输入信号时,当检测到任意一路输入信号状态发生变化时即执行延时程序,在执行延时程序的过程中将检测不到其他输入状态的变化,所以能够识别的动作间隔不可能小于延时时间T,特别是当多路输入信号的状态集中在短时间内变化时,电路的性能会严重下降。并且,由于频繁执行延时程序,会影响系统的效率和实时性。

2判决滤波

判决滤波是一种基于概率统计的滤波方法。在采样时钟CLK的控制下,每隔时间t对开关信号进行一次采样,并对时间T0内采集到的n个采样值进行判断( n = T0 /t),如果这n个采样值中高电平‘1’的个数百分比大于X,则输出高电平;相反,如果低电平‘0’的个数百分比大于X,则输出低电平。

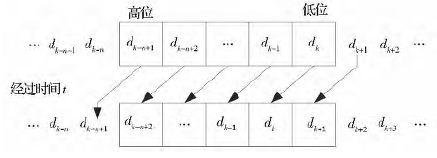

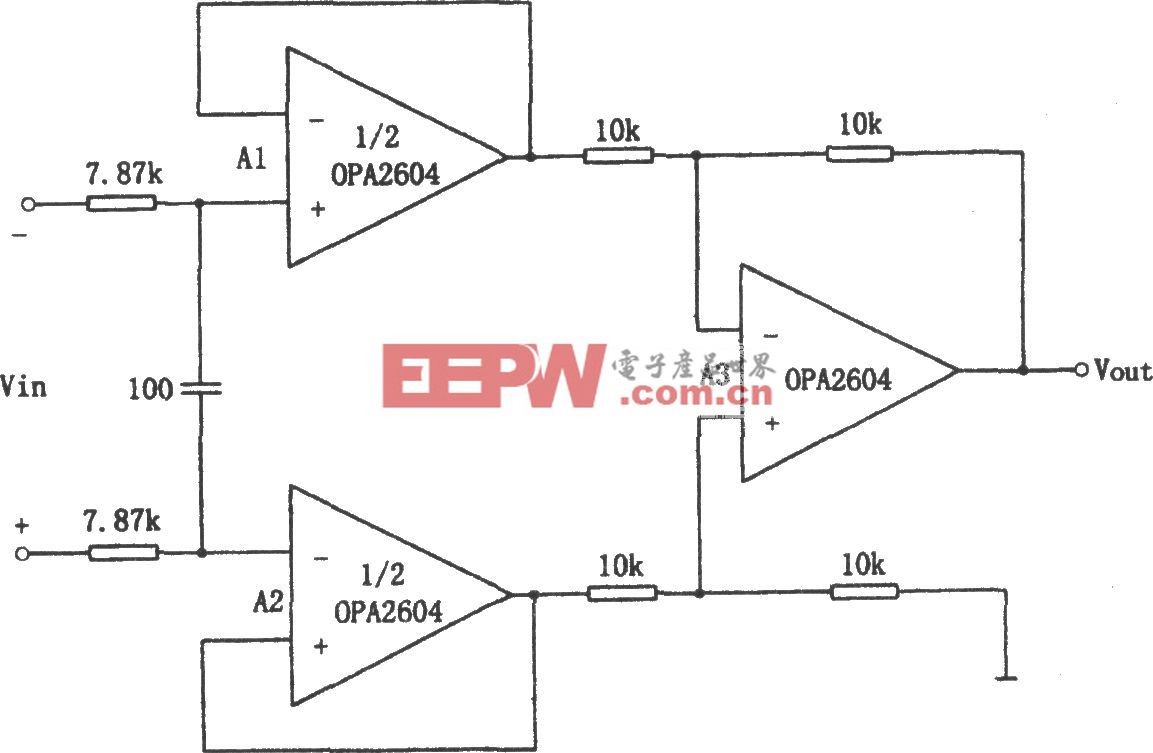

采用一个n位寄存器来实现判决滤波,寄存器各个位的值依次为采样得到的n个采样值。寄存器的模型如图6所示。

图6寄存器模型

在图6中,n个格子分别代表寄存器的n个位,寄存器左侧的数据为已经处理过的数据,寄存器内的n个数据为正在处理的数据,寄存器右侧的数据为即将处理的数据。每过一个采样时间间隔t,数据依次向高位滑动一位,最低位赋值为输入信号当前的状态值。

如上述过程,寄存器内的数据在不断地更新,数据每滑动一次,即对n个采样值进行一次判断,从而达到滤波的目的。由于干扰脉冲的随机性,采到高电平和低电平的概率是相等的,所以,作为判断依据的百分比X不能小于50%.在实际应用中,为了使滤波更可靠,X的取值一般都大于50%.

2. 1判决滤波程序设计

本设计采用一个9位寄存器( n = 9),每次判断时只要‘1’的个数大于或等于5,则滤波输出‘1’,否则输出‘0’( X = 5 /9)。图7为判决滤波程序的流程图。

图7判决滤波程序流程图

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理 脉冲点火器相关文章:脉冲点火器原理 数字滤波器相关文章:数字滤波器原理

评论