【从零开始走进FPGA】随心所欲——DIY 系统板

3. EPM240T100C5N 核心板设计

本文引用地址:http://www.eepw.com.cn/article/268272.htm(1)电源模块

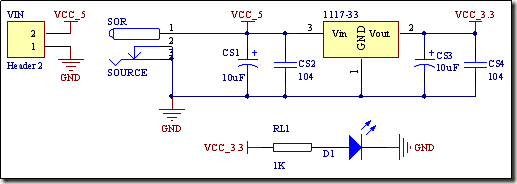

a) 由于CPLD内核工作需要3.3V电压,因此电源模块需要能提供3.3V电源,由AMS1117-3.3直接产生,供给FPGA VCCIO。电路图如下所示:

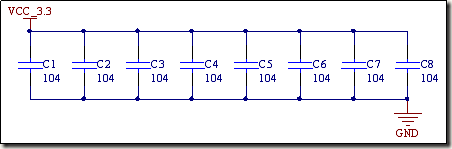

b) 由于PLD工作频率之高,为了得到更稳定的时候,更稳定的工作状态,提供更稳定的电源,需要在每个VCC接口下拉一个104的电容。如下图所示:

关于并联电容有如下作用:

此处为去耦电容,去藕电容就是起到高频信号提供回流路径,就是去除高频耦合,满足驱动电路电流的变化,避免相互间的耦合干扰 ;同时也有滤波的作用(根据TI的模拟设计方案,若是几百兆的频率工作,最好同时并联103一下的电容,已达到更好的状态)。

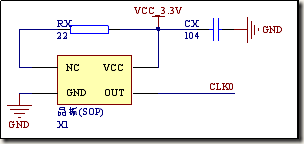

(2)时钟模块

时钟是CPLD工作的必须条件(除非在要求不高的场合,使用内部UFM),用50MHz的晶振产生时钟源,供给CPLD,作为驱动时钟。其电路如下所示:

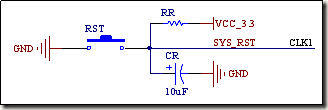

(3)复位模块

考虑到电路的稳定性,工作的可控性,在电路板中一般都设定复位模块,来实现硬件的异常复位或者重新开始工作。具体电路图如下所示:

注意:复位信号与CPLD的全局时钟输入IO相连,这并不意味着只能连全局时钟,只是全局时钟连接能够达到更大的同步性以及可控性,而一般IO是具有局部性,在时序要求相当严格的场合,这样更保险。

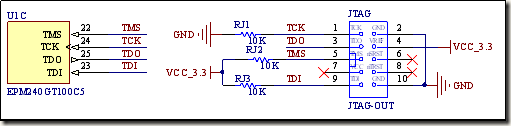

(4)JTAG模块

保证一个模块的运行,这理所当然需要一个灵魂。而这个灵魂的通道,就是JTAG接口。JTAG和PC通信,烧录配置信息。具体电路图如下所示:

4. CPLD核心板Layout注意事项

(1)每一个VCC的去耦电容要尽可能靠近端口,以达到更好的去耦效果

(2)JTAG接口4条信号线,大致保持等长,保证信号完备性

(3)晶振尽可能靠近IC,CLK输入信号线不能与IO信号线平行

(4)电源尽量做到数模隔离,减少干扰

(5)必要时加上防短路电路

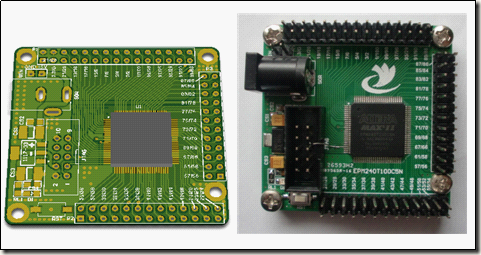

5. CPLD核心板实物图

若有需要参考原理图的读者,请下载Bingo设计的原理图,下载地址为:

http://www.chinaaet.com/lib/detail.aspx?id=86263

注:原理图见附件。

1. EP2C8Q208C8N 引脚 介绍

Cyclone II数据手册下载地址:http://www.altera.com.cn/literature/lit-cyc2.jsp

EPM2C8Q208C8 引脚介绍:

相对于CPLD而言,此款型号FPGA出了引脚上增多外,多了1.2V内核电压,ASP接口,两个锁相环,以及配置方式选择引脚 MSEL。

2. EP2C8Q208C8N 工作条件

(1)VCC1 = 3.3V,VCC2 = 1.2V, GND = 0V

(2)8个CLK全局时钟接口至少有一个输入作为驱动时钟

(3)JTAG接口,用来配置FPGA

(4)ASP接口,用来烧录EPCS

(5)MSEL,用来选择工作模式(同时接地为JTAG+ASP模式)

注意1:(4)不是必须的,可以间接通过JTAG下载jic文件来配置EPCS。

注意2:对于Cyclone IV器件而言,除了IO,PLL增加以外,另需2.5V芯片工作电压;以及JTAG保护电路。

DIY机械键盘相关社区:机械键盘DIY

fpga相关文章:fpga是什么

晶振相关文章:晶振原理

评论