基于FPGA的PCI接口设计

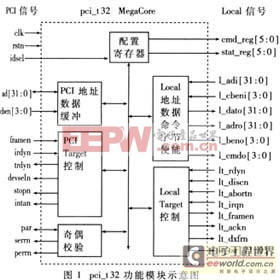

Pci_t32内部功能模块及周边信号如图1所示。

左侧PCI信号是符合PCI规范的标准信号,在这里不多加解释。下面重点介绍右侧用户逻辑接口local信号:

L_aci 31 0 ,local侧地址、数据输入信号。

L_cbeni 3 0 ,local侧命令、字节使能输入信号,位定义及时序符合PCI规范。

L_dato 31 0 ,local侧数据输出信号。

L_adro 31 0 ,local侧地址输出信号。

L_beno 30 ,local侧字节使能输出信号,位定义及时序符合PCI规范。

L_cmdo30,local侧命令输出信号,位定义及时序符合PCI规范。

Lt_rdyn,local侧目标设备准备好信号(target ready),对pci_t32是输入信号。

Lt_discn,local侧目标设备通过置低该信号请求pci_t32向PCI 侧主设备发出断开连接信号(disconnect request),对pci_t32是输入信号。

Lt_abortn,local侧目标设备通过置低该信号来请求pci_t32向PCI 侧主设备发出放弃操作信号,对pci_t32是输入信号。

Lt_irqn,local侧目标设备中断请求信号,对pci_t32是输入信号。

Lt_framen,PCI主设备通过pci_t32读写local侧目标设备时,pci_t32置低该信号(输出信号).

Lt_ackn,当为目标写操作时,PCI_t32置低该信号(输出信号),表示数据有效;当为目标读操作时,PCI_t32置低该信号(输出信号),表示已准备好读数。

Lt_dxfrn,输出信号,表示local 目标设备数据传输成功。

Lt_tsr 11 0,输出信号,控制local目标设备状态寄存器。

Cmd_reg 5 0,配置命令寄存器输出信号。Bit0,I/O操作使能;bit1,Memory操作使能;bit2,保留;bit3,memory写无效使能;bit4,奇偶校验出错响应使能;bit5,系统出错响应使能。

Stat_reg 5 0 ,配置状态寄存器输出信号。

3 读写操作时序分析与设计要点

pci规范中定义了两种读写操作,即Memory和I/O的读写。Pci_t32的读写操作包括:32位的Memory单周期读写、Memory猝发读写、I/O单周期读写以及配置读写。Pci_t32 的Memory读写分为单周期和猝发两种模式,而I/O的读写只有单周期模式。所谓猝发模式,即在给出首地址后,主设备连续读写多个数据,用户设备应能对首地址自动加1。配置读写是指pci主设备对pci_t32的配置空间寄存器进行读写操作,pci主设备与pci_t32之间的接口是无缝连接。本文只分析32位Memory单周期读写时序,其它模式的读写时序大同小异,此略。

3.1 Memory 读操作

pci_t32的单周期memory read操作时序如图2所示。

时序分析及用户逻辑设计要点:pci主设备在第2个clk给出要读的目标地址ad 31 0 和Memory读命令cben 3 0 =6,pci_t32在第3个clk向用户设备给出读目标地址1_adro 31 0和Memory读命令l_cmdo 3 0 =6。用户设备要对l_cmdo 3 0 译码来判断是何种操作,对l_adro 31 0 译码来选择目标地址。在lt_framen输出为低的下个时钟周期,若用户设备逻辑准备好要输出的数据,可以置低lt_rdyn。若用户逻辑没有准备好,可以延迟置低lt_rdyn来产生延时等待周期。当lt_dxfrn输出为低电平时(第6个clk),pci用户设备必须将目标地址的数据D0放到l_adi 31 0 ,用户逻辑可以用lt_dxfrn来作为存储单元的输出使能信号(/Output Enable)。这样,在第7个clk的上升沿pci_t32可以采样到数据D0。在第8个clk的上升沿pci主设备可以得到数据D0。

评论