PCI总线技术概论

从数据宽度上看,PCI总线有32bit、64bit之分;从总线速度上分,有33MHz、66MHz两种。目前流行的是32bit @ 33MHz,而64bit系统正在普及中。改良的PCI系统,PCI-X,最高可以达到64bit @ 133MHz,这样就可以得到超过1GB/s的数据传输速率。如果没有特殊说明,以下的讨论以32bit @ 33MHz为例。

一、基本概念

不同于ISA总线,PCI总线的地址总线与数据总线是分时复用的。这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输。在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI设备做目标(从设备,Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定在谁有权力拿到总线的主控权。

32bit PCI系统的管脚按功能来分有以下几类:

系统控制: CLK,PCI时钟,上升沿有效

RST ,Reset信号

传输控制: FRAME#,标志传输开始与结束

IRDY#,Master可以传输数据的标志

DEVSEL#,当Slave发现自己被寻址时置低应答

TRDY#,Slave可以转输数据的标志

STOP#,Slave主动结束传输数据的信号

IDSEL,在即插即用系统启动时用于选中板卡的信号

地址与数据总线: AD[31::0],地址/数据分时复用总线

C/BE#[3::0],命今/字节使能信号

PAR,奇偶校验信号

仲裁号: REQ#,Master用来请求总线使用权的信号

GNT#,Arbiter允许Master得到总线使用权的信号

错误报告: PERR#,数据奇偶校验错

SERR#,系统奇偶校验错

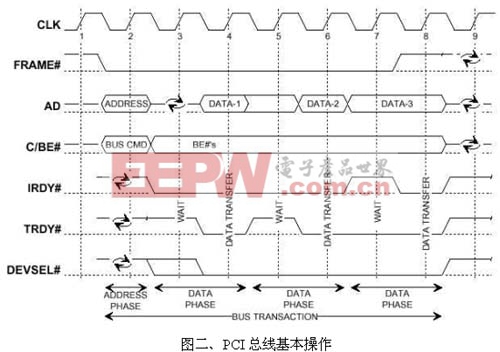

当PCI总线进行操作时,发起者(Master)先置REQ#,当得到仲裁器(Arbiter)的许可时(GNT#),会将FRAME#置低,并在AD总线上放置Slave地址,同时C/BE#放置命令信号,说明接下来的传输类型。所有PCI总线上设备都需对此地址译码,被选中的设备要置DEVSEL#以声明自己被选中。然后当IRDY#与TRDY#都置低时,可以传输数据。当Master数据传输结束前,将FRAME#置高以标明只剩最后一组数据要传输,并在传完数据后放开IRDY#以释放总线控制权。

这里我们可以看出,PCI总线的传输是很高效的,发出一组地址后,理想状态下可以连续发数据,峰值速率为132MB/s。实际上,目前流行的33M@32bit北桥芯片一般可以做到100MB/s的连续传输。

二、即插即用的实现

所谓即插即用,是指当板卡插入系统时,系统会自动对板卡所需资源进行分配,如基地址、中断号等,并自动寻找相应的驱动程序。而不象旧的ISA板卡,需要进行复杂的手动配置。

实际的实现远比说起来要复杂。在PCI板卡中,有一组寄存器,叫"配置空间"(Configuration Space),用来存放基地址与内存地址,以及中断等信息。

以内存地址为例。当上电时,板卡从ROM里读取固定的值放到寄存器中,对应内存的地方放置的是需要分配的内存字节数等信息。操作系统要跟据这个信息分配内存,并在分配成功后把相应的寄存器中填入内存的起始地址。这样就不必手工设置开关来分配内存或基地址了。对于中断的分配也与此类似。

评论