基于DSP和FPGA的视频编码器

3 测试结果

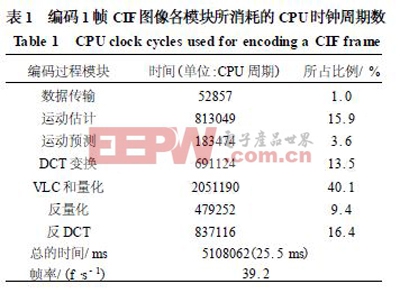

表1为编码器进行装载测试的测试结果(1帧的平均值)。装载测试是首先将视频测试序列装载到编码器的SDRAM中,然后进行压缩编码。使用的视频序列为标准测试序列mother(CIF格式,彩色,YUV4∶2∶0,5帧),DSP主频设置为200MHz。

表2为美国TI(TexasInstrument)公司基于DSK6711EVM板开发的H.263视频编码器的性能测试数据(装载测试)[6],DSP主频为150MHz。TI公司针对DSK6711对H.263做了全面优化,算法关键代码采用了线性汇编语言编写。H.263视频编码算法与MPEG视频编码算法的压缩编码原理、过程和计算复杂度大致相当,因此二者具有可比性。

从表1和表2可以看出,研制的视频编码器平均压缩帧率为39.2f/s(CIF图像),而TI公司开发的视频编码器平均压缩帧率为20f/s(CIF图像),绝对性能提高了96%,考虑到DSP主频的因素,相对性能仍然提高了47%。

4 结论

采用DSP和FPGA协同技术设计实现了一个高性能的MPEG24视频编码器。使用FPGA完成编码器I/O功能,使用DSP进行视频压缩编码,二者能够很好地并行工作,系统设计结构简捷,硬件工作可靠。同时,针对DSPC6201片内资源特点优化了视频压缩的数据流模式,采用MTJBSC算法有效地降低了压缩算法的计算复杂度。测试结果表明,采用MPEG24视频标准该视频编码器每秒能够每秒压缩39.2帧CIF图像。

评论