基于改进型二步索引算法OSD电路的FPGA

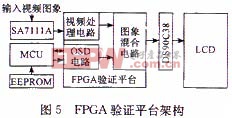

设计在Xilinx公司的ISE6.3软件环境下,使用Verilog HDL硬件描述语言对其电路逻辑进行描述,并以Xilinx公司xc2v1500bg575-4型为核心芯片的FPGA仿真验证平台对其进行硬件实现及功能验证。FPGA验证平台架构如图5所示。

验证平台输入模拟视频信号,经SAA7111A芯片电路A/D采样转变为数字视频信号接入FPGA验证平台。经过视频处理电路去隔行、尺寸缩放等处理的视频信号在图象混合电路中与OSD菜单混合后输出经DS90C38芯片电路转为LVDS(低压差分信号)信号并驱动液晶屏显示结果。

对2种字符索引算法下实现的OSD电路进行验证比较。OSD字符索引电路部分使用到的存储器资源可以分为字符编码存储器、行字符数存储器、字符行寄存器3种。以生成图6中所示菜单为例分析2种算法下OSD字符索引电路对存储器资源的使用情况,将结果列于表1中。

从表中可以看出,以二步索引算法实现的字符索引电路使用了8个bytes的行字符数存储器和1个byte的字符行寄存器,而以逐字索引算法实现的字符索引电路在这2类存储器上的使用量均为0。但是,后者在字符编码存储器的使用上却达到了96 bytes,远远多于前者50 bytes的使用量。从表1中可以看到,前者对存储器资源的总使用量比起后者减少了很大一部分。随着菜单尺寸的增加和显示的字符信息的增加,二次索引算法对存储器资源的节省效果也会更加的显著。

4 结束语

采用模块化设计方法实现的OSD电路,作为视频格式处理芯片的子电路模块,对硬件资源的使用将影响到整块芯片的电路性能。本文针对OSD电路中以存储器为硬件资源的主要开销这个特点,提出了采用二步索引算法实现的一种改进型字符索引结构的OSD电路。引入字符行寄存器和行字符数存储器,通过对行字符数和字符编码的二步索引,从而得到了菜单的显示信息,同时大大地降低了对存储器资源的使用。该算法的硬件结构简单,易于实现,在实现了同样的电路功能的前提下,大大节省了硬件资源的开销。

本文所介绍的基于二步索引算法实现的改进字符索引结构的OSD电路,将作为子模块电路集成于一款视频格式转换多媒体芯片的系统中,为其提供人机交互功能。该系统可应用于汽车电子、视频显示等多媒体处理场合。

评论