一种基于FPGA的数字复接系统的设计与实现

引言

数字通信网中,为扩大传输容量和提高传输效率,常运用数字复接技术,将若干低速码流合并成高速码流,通过高速信道传送。而以往的PDH数字复接系统大多采用模拟电路或传统ASIC设计,电路复杂庞大且受器件限制,灵活性和稳定性都很低,系统的调试修改难度也很大。近年来可编程器件的应用日益广泛,使用较多的是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。FPGA器件性能优越,使用方便,成本低廉,投资风险小,使用FPGA设计可以完全根据设计者需要开发ASIC芯片,可方便地反复编写和修改程序,即使制成PCB后仍能进行功能修改。本文将着重介绍运用FPGA技术实现基群与二次群之间复接与分接系统的总体设计方案。

数字复接基本原理及系统构成

二次群帧结构及其复接子帧结构

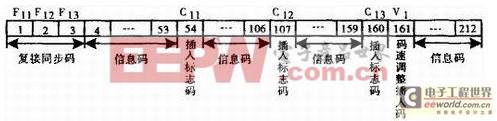

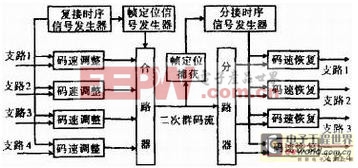

按ITU-TG.742协议,工作在8448kbit/s的采用正码速调整的二次群复接设备帧结构如图1所示,一帧共有848bit,前12位帧码组包括帧同步码10位,码型为1111010000;失步对告码,同步为“0”,失步为“1”;国内通信备用码。Cj1、Cj2、Cj3(j=1,2,3,4)为插入标志码,Vj(j=1,2,3,4)为码速调整插入比特,其作用是调整基群码速。二次群由四支路的子帧构成,子帧结构如图2所示,一子帧有212bit,1、2、3位码为帧码组,记Fj;插入标志码用Cj表示;码速调整插入比特用Vj表示。

图1 二次群帧结构

图2 复接子帧结构(以第一条支路为例)

复接系统构成

复接系统构成的框图如图3。复接时序信号发生器产生码速调整需要的时序信号,四路基群信号先各自经正码速调整,变为2.112Mbit/s的同步码流。合路器顺序循环读取四路码流,并在每帧开头插入帧定位信号,输出8.448Mbit/s的标准二次群。

图3 复接的系统构成框图

在接收端,合路码流先进行帧定位捕获,判定系统处于同步态、失步态还是过渡态。一旦捕获到帧定位信号,便驱动分接时序信号发生器工作,产生分路和码速恢复需要的时序信号,同时分路器工作,把帧定位信号抛掉,顺序循环分别送入4个码速恢复单元,扣除插入码元,恢复成四路2.048Mbit/s的基群信号。

评论