基于FPGA的大屏幕全彩LED扫描控制器设计

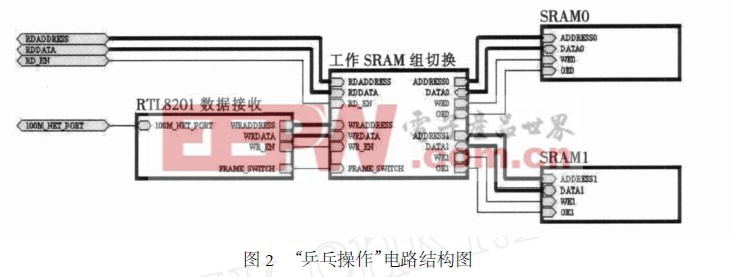

由于LED 显示屏包含4 列相互独立的显示模块,因此扫描控制电路需要提供4 路RGB 数据输出接口, 在图1 中表示为RGB0 ~ RGB3 。

CLOCK_OUT 为移位时钟信号输出端口,RGB0~RGB3 在该时钟的上升沿有效,各个端口的红、绿、蓝三色显示数据通过时钟脉冲信号分别逐位移入驱动芯片的显示缓存。LA TCH 信号为串行数据输出结束后需要进行显示刷新时的锁存脉冲。EN 为灰度控制信号,当EN 有效时,L ED 可以随输入数据的0 、1 状态熄灭或者点亮,其有效时间宽度对应为表2 所示的点亮时间。

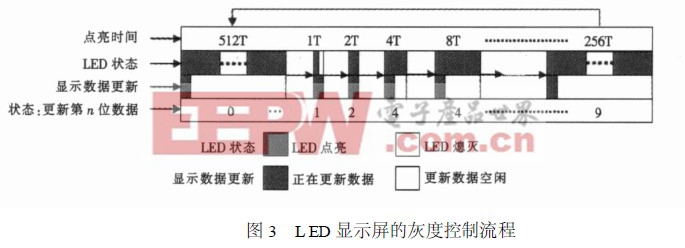

EN 信号产生模块为实现灰度图像显示的重要模块,该模块将输入的位计数值转换成为对应位的点亮时间,并进行相应时间长度的亮度控制。

在本设计中,输入的灰度信号为256 级,考虑到反γ非线性校正过程引起的灰度损失,将输出的灰度级别定义为1 024 级,因此需要得到10 位灰度数据各个位对应的点亮时间。依据“灰度实现原理”,10 位灰度数据各个数据位对应的点亮时间从D0 ~D9 分别从1 T 倍增为512 T ,点亮总时间为1 023 T 。

由于驱动板中驱动芯片有二级缓存功能,所以更新数据和点亮L ED 这两个控制过程可以部分重叠,从而得到图3 所示的LED显示屏灰度控制流程。更新第0 位数据时点亮时间为512 T 、更新第1 位数据时点亮时间为1 T ...依次类推,更新第n 位数据时,控制点亮的时间为上一次所更新的位所需要的点亮时间。

4 结论

讨论了一种大屏幕全彩L ED 显示屏设计的扫描控制器设计方案,通过对“19 场扫描”实现方法的分析,针对其不足之处,提出了一种新式的逐位点亮灰度控制方法。该控制方法使得在全彩LED 显示屏的设计中,可以在L ED 的发光效率和刷新率之间进行灵活的调整。本设计采用FP2GA 控制芯片为设计平台来完成扫描控制电路的实现,借助EDA 开发工具,降低了驱动电路的设计难度,缩短了项目的开发周期。

评论