基于FPGA的速率自适应图像抽取算法

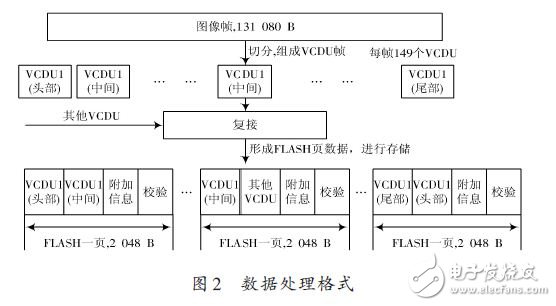

FLASH的读写都基于页进行操作,读出一页的两个VCDU中,有多种可能性,数据处理过程如图2 所示,图2中给出三种可能,一是前一个是需要抽取的头数据,后一个是需要抽取的中间数据;二是前一个是需要抽取的图像数据,后一个是不需要抽取的其他 VCDU 数据;三是前一个是需要抽取的尾数据,后一个是下一幅图像的头,但不需要抽取。

本文引用地址:http://www.eepw.com.cn/article/221482.htm

可见,在抽取回放中必须滤除一定数据,保证抽取图像的完整性和正确性,因此在存储时增加附加信息,以解决图像完整性问题。

附加信息设计为6 b,格式定义见表1.

附加信息与数据一起被存到存储芯片中。在回放时,读取附加信息,解析出高VCDU有效/无效信号和低VCDU有效/无效信号。由回放请求模块进行数据滤除,保证仅回放有效数据,并且为完整图像。

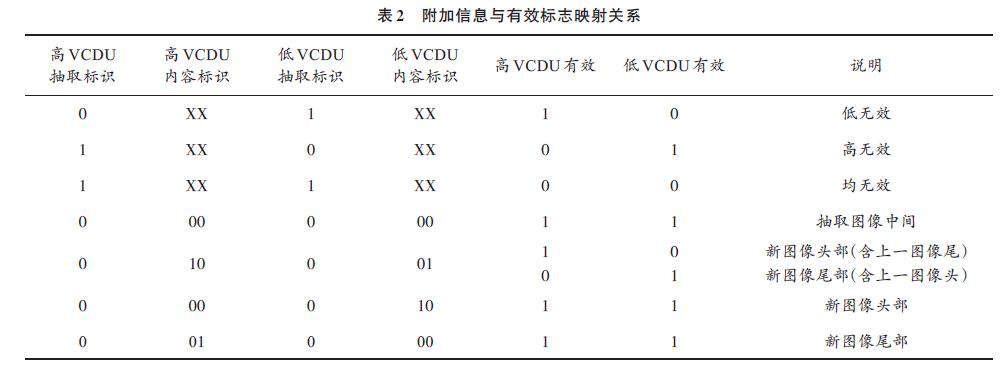

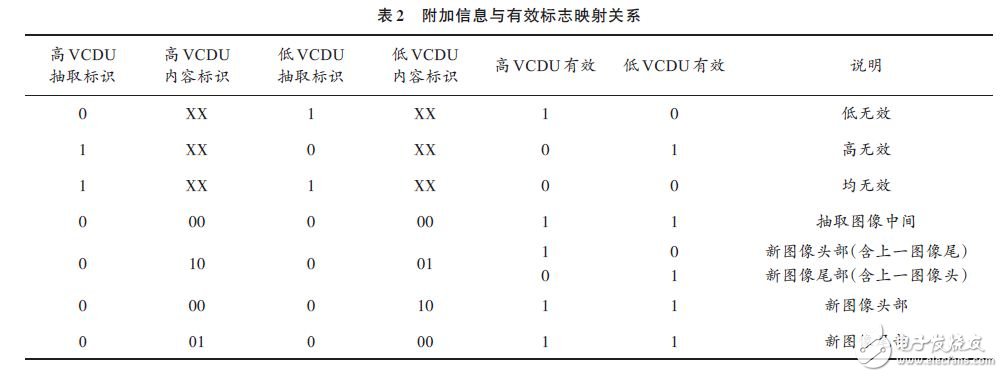

附加信息与有效标志映射关系见表2.对输入数据的各种情况,按照表2中映射关系解析出有效/无效信号。

数据过滤模块设置缓存,根据高低VCDU有效标示控制缓存地址,为1进行读取,为0跳过无效的VCDU数据,实现数据的滤除。

1.2 实时性设计

方法中必须获取到帧头VCDU 信息和帧尾VCDU信息才会更新图像数据帧地址寄存器,即在收到一整幅图像之后才能进行回放。

抽取的延时计算一幅图像第一比特输出和输入时间之差,最坏情况时第N 幅图像已经写入,第N + 1 幅图像尾部没有写完,即在第N 幅图像头写入后两幅图像时间才开始回放。抽取过程中延迟时间=两幅图像时间+数据回放时间。工程中,图像生成速率为10幅/s,一幅图像的生成时间按 100 ms计算。

回放数据的时间为数据从FLASH芯片中读出时间和数据缓存时间,每页2 KB,读取时间约320 μs;其余处理路径上的寄存时间《10 μs.因此,抽取过程中延迟时间约为200.33 ms ,完全可以满足图像的回放观看需要。

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

评论