基于ADS1298与FPGA的高性能脑电信号采集系统

3 软件模块设计

本文引用地址:http://www.eepw.com.cn/article/221427.htm3.1 FPGA内部信号处理控制模块设计

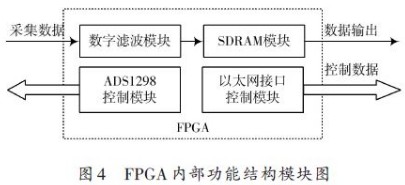

本系统使用Verilog HDL语言单独编写A/D转换器的控制模块、SDRAM存储器控制模块、数字滤波器模块以及以太网端口传输控制模块,通过功能仿真和时序仿真来验证各个模块是否能够独立完成相对应的控制功能。验证成功后,最终通过例化,在FPGA内部形成一个脑电信号采集系统的核心处理控制模块,图4为核心处理控制模块的具体功能结构模块框图。

3.2 ADS1298软件设计

本系统中最重要的一环就是模/数转换,这里重点介绍ADS1298的软件模块设计。ADS1298的工作流程主要包括:上电初始化、发送操作命令和配置寄存器、开始转换并读取转换数据。ADS1298的操作命令主要分为数据操作命令和寄存器读写命令。数据操作命令主要包含SDATA和RDATAC(连续读数据)。连续读数据只需要写入一次RDATAC 操作命令,就可以在每次的DRDY变为低电平时读取转换数据。寄存器读写命令分为RREG 和WREG.这两个操作命令分别包含两个字节,第一个字节为读写寄存器的起始地址,第二个字节为读写寄存器的个数。

FPGA 软件编程中具体的ADS1298 模块内部框图如图5所示。

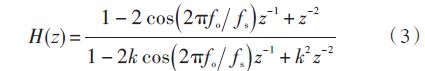

3.3 数字滤波模块软件设计

本系统的数字滤波模块主要为50 Hz 陷波器和数字带通滤波器,两者的软件设计方法相似,这里重点介绍50 Hz 的陷波器设计方法。本系统中设计的陷波器技术指标为:抽样频率fs 为1 kHz,陷波频率fo 为50 Hz,3 dB 带边频率为45 Hz和55 Hz,阻带上下边频率为49 Hz和51 Hz,阻带衰减不小于40 dB.为了便于硬件的实现,本文选用二阶的IIR 陷波器,其传递函数如式(3)所示:

k 的值决定了陷波深度,根据具体的信号进行调整,从而实现最佳陷波。对于EEG信号,最佳的k 取值为0.88.FPGA软件设计时需要根据传递函数设置几个寄存器存储系数和中间值,并在每个时钟对这些中间值移位更新,然后重新计算得到新的输出值。

4 结语

系统采用Altera Cyclone Ⅱ系列芯片EP2C35F672作为控制和处理的核心,8通道、低噪声、低功耗、24位的Σ-△模/数转换芯片ADS1298作为采集系统核心,简化了系统的硬件设计,具有功耗低、便携式、精度高等优点;采用FPGA和DM9000A以太网控制器相结合,成功的将脑电信号采集系统和PC上位机相连,避免了直接上传时的数据丢失,实现了彼此间的高速数据通信。本系统利用Quartus Ⅱ工具和Verilog HDL 语言对FPGA进行设计、仿真和验证,便于设计的修改和优化,大大缩短了产品的开发设计周期,因此本系统具有良好的使用价值和应用前景。

模拟信号相关文章:什么是模拟信号

fpga相关文章:fpga是什么

模数转换器相关文章:模数转换器工作原理

评论