用单片机控制DDS实现短波跳频系统的调制

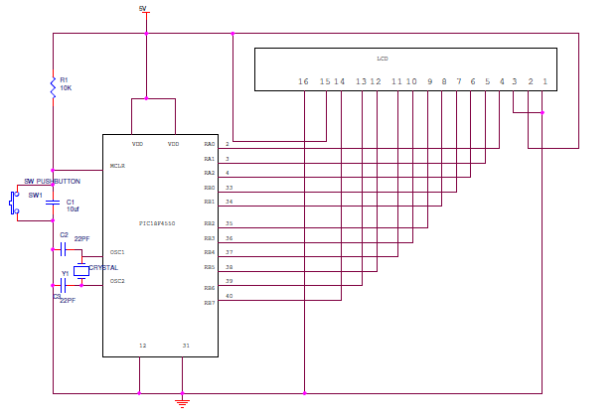

本系统的调制电路是用51系列的单片机89C51 控制DDS芯片AD7008 来完成的。如图2所示,通过D0~D7数据总线在WR、CS的控制下,将数据控制字首先写入AD7008的并行寄存器,然后在LOAD和TC0~TC3的控制下按表2所示将并行寄存器数据转载到功能寄存器。

表2 AD7008外部控制逻辑(并行方式)

| TC3 | TC2 | TC1 | TC0 | LOAD | 源寄存器 | 目的寄存器 |

| X | X | X | X | 0 | -- | -- |

| 0 | 0 | X | X | 1 | 并行寄存器 | 命令寄存器 |

| 1 | 0 | 0 | 0 | 1 | 并行寄存器 | 频率寄存器0 |

| 1 | 0 | 0 | 1 | 1 | 并行寄存器 | 频率寄存器1 |

| 1 | 0 | 1 | 0 | 1 | 并行寄存器 | 相位寄存器 |

| 1 | 0 | 1 | 1 | 1 | 并行寄存器 | IQ寄存器 |

使用AD7008内部参考电压(VREF=1.27V),RSET≈390Ω时为满刻度电流输出。在管脚IOUT与地之间接入50Ω电阻,输出信号峰-峰值为1V的跳频信号。P1.0,P1.1分别控制芯片复位和频率寄存器的选择。根据电路,RAM6116地址为0000H~07FFH,并行寄存器地址为4000H,命令寄存器地址为8000H,频率寄存器0地址为0A000H,频率寄存器1地址为0A800H,相位寄存器地址为0B000H,IQ寄存器地址为0B800H。相位寄存器的值为差分相位,0、π/4、π/2、3π/4、π、5π/4、3π/2、7π/4分别对应寄存器的值(低12位)为:000H、200H、400H、600H、800H、0A00H、0C00H、0E00H。跳频信号的跳频定时由定时器0中断来实现:跳频速率2560跳/秒,定时时间为390.625μs。

3 程序实现

该调制系统的软件流程图如图3所示。

跳频信号的调制关键是跳频码的发生和DDS的控制。短波FH/DQPSK系统要求有良好特性的跳频序列,混沌理论的发展为跳频序列的产生提供了一种新的方法。利用混沌非线性来产生跳频序列,其跳频图案的性能比较好。文献[4]介绍了用单片机实现Logistic混沌FH序列的发生。目前,混沌序列的研究主要是硬件实现的有限字长问题。我们用单片机实现基于Lempel-Greenberger模型(简称L-G模型)[5]的m序列,选取周期为63,并可以为用户提供不同的m序列。它可以用于通信开始时采用短码引导长码[6]的混沌初值传递的跳频同步捕获系统(必须对m序列进行宽间隔处理以适合短波跳频系统)。图4是示波器显示的基带跳频信号波形。

以上讨论了以单片机控制DDS技术为核心实现跳频信号的调制设计方法,编写了部分实验程序。在系统的调试中发现,示波器显示波形出现相位没有正确调制在某一跳频点上,信号先在新跳频频率上以正弦波(选同相输出)形式出现一定时间,当新的相位移至DDS的相位寄存器后才使信号有新的相位。经分析得知,这是由于AD7008芯片从并口寄存器的数据转移至频率与相位寄存器没有同时进行的缘故。这可以更换其它DDS芯片来解决,如AD9850 [7],其频率和相位数据可以同时输入(频率字为32bit,相位字为5bit,休眠、厂家测试控制字为3bit,共40bit),来控制实现高速DDS技术。另外,实现的仅为数字信号的基带跳频信号调制,还必须进行二次调制成短波单边带(SSB)信号才能发射出去。如果采用更高输出最高频率的DDS芯片,即可实现短波跳频信号的一次性调制。随着制造工艺的提高,这是能够实现的。目前DDS芯片已做到1GHz以上。更好的办法是采用DDS与锁相环(PLL)技术相结合来实现,它具有较高的频率稳定度、准确度和分辨力,并具有体积小、功耗低、操作方便等特点。

评论