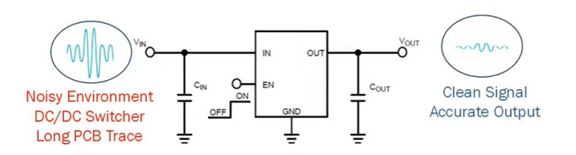

单电源供电的全差分斩波运放电路

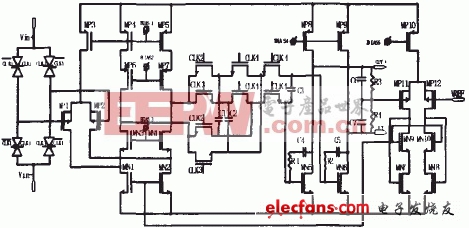

图2 斩波运放的电路结构

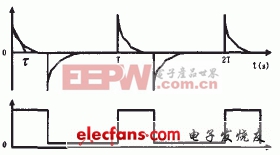

输入斩波开关完成对音频信号的调制作用,斩波开关在时钟上沿和下沿都会引入残余电压失调,图3为零输入时残余失调电压的波形。

图3(a)残余失调电压(b)斩波信号

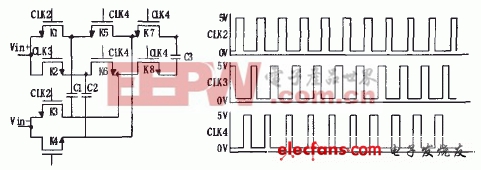

图4 T/H解调及控制时序

通过对CMOS开关特性分析可以得出等效输入残余失调电压为Vos,rmts=2Vspiketfch,其中t是MOS开关的时间常数,从此式可以看出消除残余电压失调有三种方法:

1.降低斩波频率:

2.减小输入电阻;

3.减小斩波开关的电荷注入效应。

由于MOS管1/f噪声的拐角频率一般都在几十KHz以上,减小斩波频率不能很好地对1/f噪声进行调制,而输入电阻只与信号源内阻有关,在设计中很难将输入电阻降低,因此只能考虑减小开关的电荷注入效应。为此输入斩波开关采用互补时钟结构,在尺寸上使用最小线宽,一方面能够减小传输的导通电阻,提供较大的电压摆幅;另一方面减小了电荷注入和馈通的影响,降低了残余电压失调。考虑到PMOS管比NMOS管的1/f噪声特性好,所以输入管MP1和MP2采用大面积的PMOS管,既能减小因器件的失配引起的电压失调,又可以降低晶体管1/f噪声的拐角频率,改善运放的噪声特性。

为了更小地降低残余电压失调,fold—cascode运放的输出采用T/H解调技术,电路结构和时序如图4。该电路的工作原理:在跟踪信号时K1~K4闭合,K5~K8断开,输出信号保持在电容C1和C2上,当电

电荷放大器相关文章:电荷放大器原理

评论