24位Σ-Δ ADC简化ECG/EKG模拟前端设计

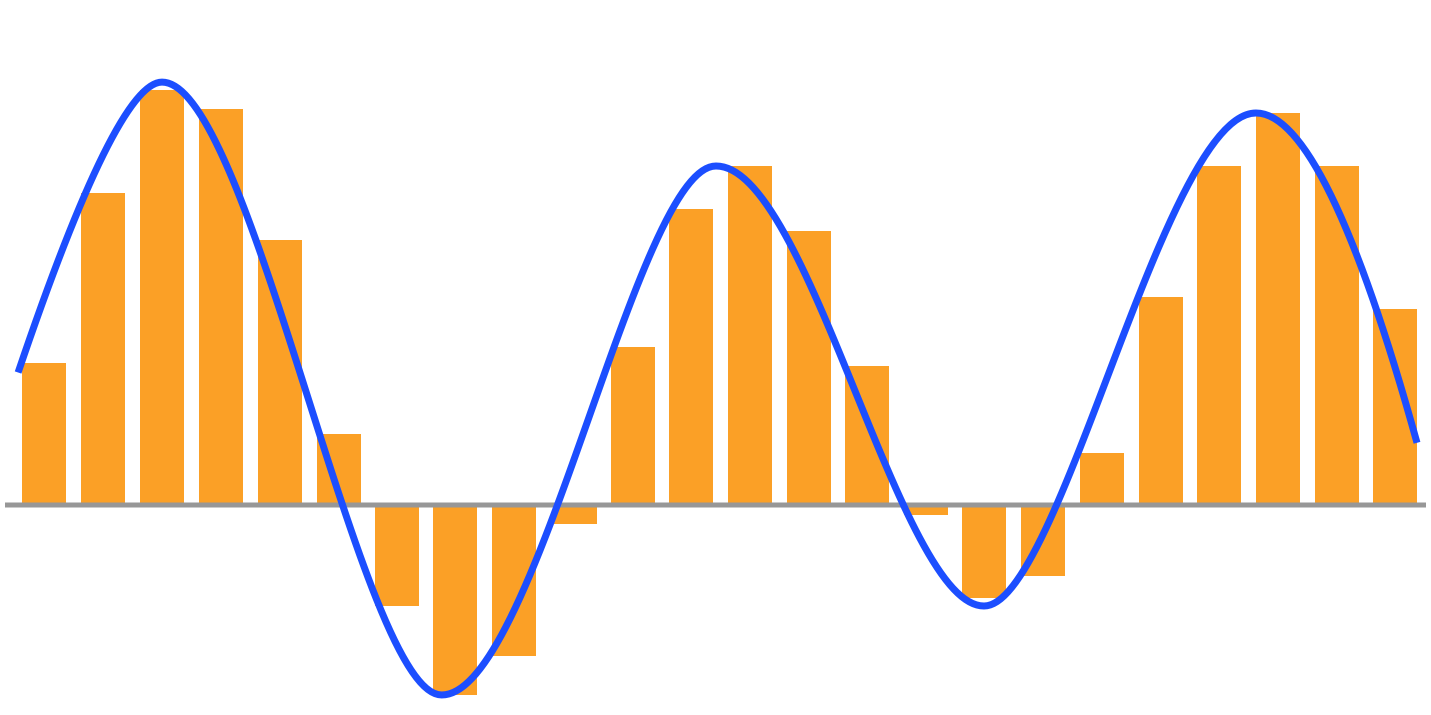

4、低通/抗混叠滤波器

低通滤波器用来抑制高频干扰,它也作为一个抗混叠滤波器(即阻止任何大于奈奎斯特或1 / 2采样频率的信号,避免产生ADC混叠)。

为了进一步降低输入共模信号,ECG设计通常还引入一级“右腿驱动器”,驱动反相共模信号返回人体。为了确保病人的安全,通常利用一个运算放大器和一个限流电阻,确保驱动到人体的是一个非常微弱的信号源。这个屏蔽装置旨在降低ECG探头承载信号的噪声耦合。

总之,ECG应用中的有用信号小于100mV,考虑到失调和共模信号,通常将其放大到2V。因此,AFE必须有2V测量范围,可以辨识低于几百,甚至几十µV的信号,采样率在1ksps左右。

正确的ADC可以减少、甚至消除对AFE的需求

AFE设计完成后,能够满足实际应用对分辨率、速率和输入量程的要求的ADC有许多。但是,仍要优先考虑具有高分辨率、高共模抑制比(CMRR)及其它优势的ADC,以确保ECG的设计需求。

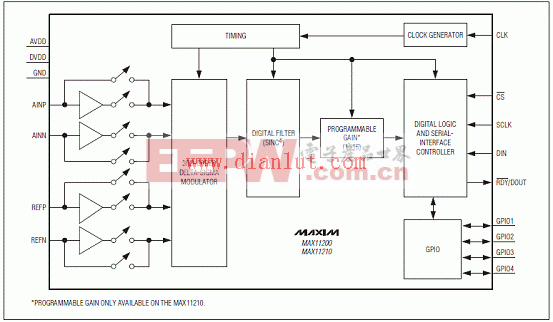

MAX11040K同步采样、Σ-ΔADC本身的性能指标即超出了此类应用的最低要求,可以取代系统的大部分功能电路,甚至可以省去AFE,提供了一种更可靠、更小封装、更简便的设计方案。

MAX11040K具备才应用的几项必备规格:

![]() 输入量程:±2.2V

输入量程:±2.2V

![]() 差分输入

差分输入

![]() 110dB共模抑制比(典型值)

110dB共模抑制比(典型值)

![]() 24位分辨率:

24位分辨率:

SNR >110dB

19位无噪声范围

有效分辨率 = 2/219 = 3.8µV

![]() ±6V输入过压保护

±6V输入过压保护

![]() 四路全差分同步采样ADC

四路全差分同步采样ADC

可级联多达32个通道同步采样

![]() 可编程输出数据速率

可编程输出数据速率

模拟信号相关文章:什么是模拟信号

滤波器相关文章:滤波器原理

滤波器相关文章:滤波器原理

高通滤波器相关文章:高通滤波器原理

评论