赛普拉斯PSoC4芯片揭秘:玩转SAR ADC模块

Cypress在2013年第二季度推出了新一代可编程片上系统PSoC4系列产品,作为PSoC(Programmable System on Chip)芯片家族中的一员,PSoC4保持了Cypress具有特色的片内可编程数字资源和丰富的模拟资源,同时由于采用ARM Cortex-M0作为处理核心,其运算性能也有显著提高。PSoC4内含许多独具匠心的功能模块,逐次逼近式模数转换器(Successive Approximation Register Analog Digital Convertor,以下简称SAR ADC)就是其中之一。本文即以SAR ADC为例,介绍如何使用PSoC4实现产品设计。

PSoC4简介

PSoC4现包含CY8C4100和CYCY8C4200两个产品系列,均采用ARM Cortex-M0作为处理核心。PSoC4具有灵活的可编程和可重新配置的模拟、数字模块,结合芯片内部灵活的互联网络,可以使用一块芯片实现复杂的混合信号设计。

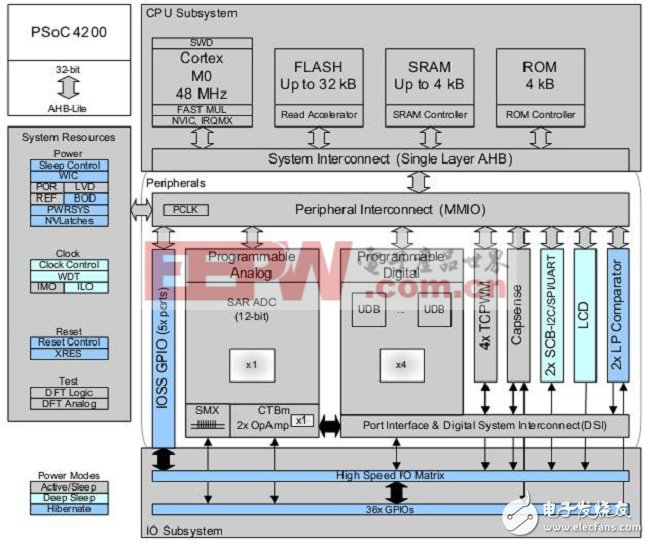

图1是PSoC4的系统框图,以下概括了其主要特性,详细内容可以参考Cypress网站上的PSoC4的数据手册。

● 48MHz ARM Cortex-M0中央处理器,支持单周期乘法

● 最大支持32KB闪存(Flash),最大支持4KB SRAM存储器

● 高达36个可灵活配置的通用输入输出管脚(GPIO),均可配置为触摸感应输入

● 两个可灵活配置驱动能力和带宽的运算放大器,可以工作在比较器模式,也可做ADC的输入缓冲器

● 一个12-bit 1M采样率的SAR ADC,支持差分和单端输入,无软件开销的输入通道切换,硬件实现的采样结果平均,采样结果范围比较

● 两个电流数模转换器(IDAC),不用于CapSense时可以输出给内部模块,或通过GPIO输出用于其他用途

● 两个内部低功耗比较器,可以在深度睡眠和休眠模式下工作,可以产生唤醒信号中断睡眠

● 一个电容感应(CapSense)模块,提供极佳的信噪比和防水功能,具有简单易用的应用设计接口

● 四个通用数字模块(UDB),每个包含两个微型的可编程逻辑阵列和一个8位数据运算单元。Cypress提供了自定义组件功能,用户可以根据设计需要,使用Verilog控制UDB实现用户定制的功能模块

● 2个可灵活配置的串行通讯模块(SCB),每个均可配置成SPI/UART/I2C,支持基于串口的LIN、IrDA、SmartCard协议

● 四个16比特的定时器/计数器/脉冲宽度调制模块(TCPWM),支持中心对齐、边沿对齐模式,伪随机模式,支持灵活的死区控制,PWM可与ADC同步,用户可自定义在PWM周期内任一时刻触发ADC转换),支持同步刷新PWM的占空比

图1:PSoC4芯片系统框图

模数转换器相关文章:模数转换器工作原理

评论