程控滤波器的设计

3.2.3 椭圆低通滤波器

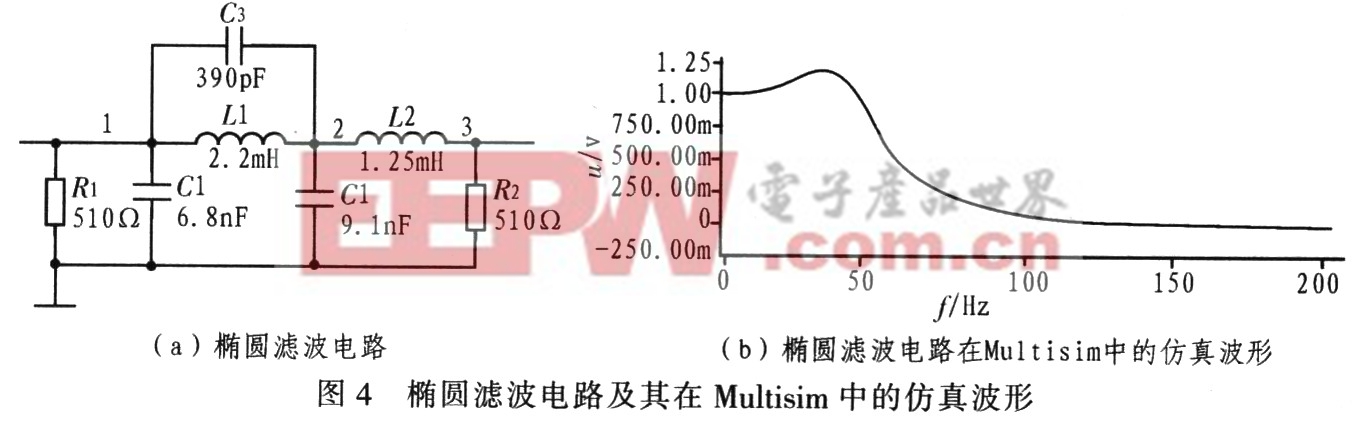

采用无源LC椭圆低通滤波器实现,从滤波器设计手册上查表得四阶椭圆无源滤波器在θ=19°,Ωs=3.311时,相应归一化参数:C1=1.210 F,C2=0.062 42 F,L2=1.220 H,C3=1.891 F,L4=0.846 9 H。取无源滤波器的端间匹配阻抗为R=510 Ω,截止频率fp=50 kHz代入公式:本文引用地址:http://www.eepw.com.cn/article/188595.htm

式中,Cn,Ln表示归一化的电容值,电感值;C'n,L'n表示以fp为通带3 dB衰减的低通滤波电路中所对应的电容值、电感值。计算结果为:C1=7.56μF,C2=390 pF,L2=1.98 mH,C3=11.81μF,L4=1.38 mH。将上述值转换为标称值后,得到图4所示的电路原理图和仿真波形。

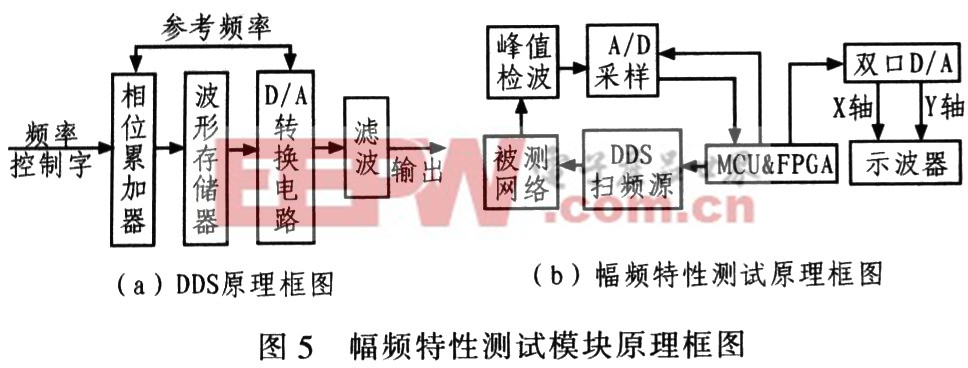

3.3 幅频特性测试模块

FPGA由DDS产生0~200 kHz范围内的扫频信号,DDS产生信号的频率稳定度较高,而且信号的频率步进和信号幅值控制方便。DDS以Nyquist时域采样定理为基础,在时域中进行频率合成。DDS的基本工作原理:每个参考频率fs上升沿到来时,N位的相位累加器值便按照频率控制字K的长度增加一次,输出所得相位值,正弦查找表将相位信息转化为相应的正弦幅度值。在fs和N一定的情况下,输出波形频率由频率控制字K决定。以一定步进循环增加频率控制字K,输出频率变化的扫频信号。

扫频信号通过被测网络后,由AD637检测有效值,即利用各个频点通过网络后的有效值在示波器上显示其幅频特性图。AD637的外围电路简单,而且当输入峰峰值大于2 V时,其测量误差在100 Hz~1 MHz的范围内可忽略。图5为幅频特性测试模块原理框图。

4 系统软件设计

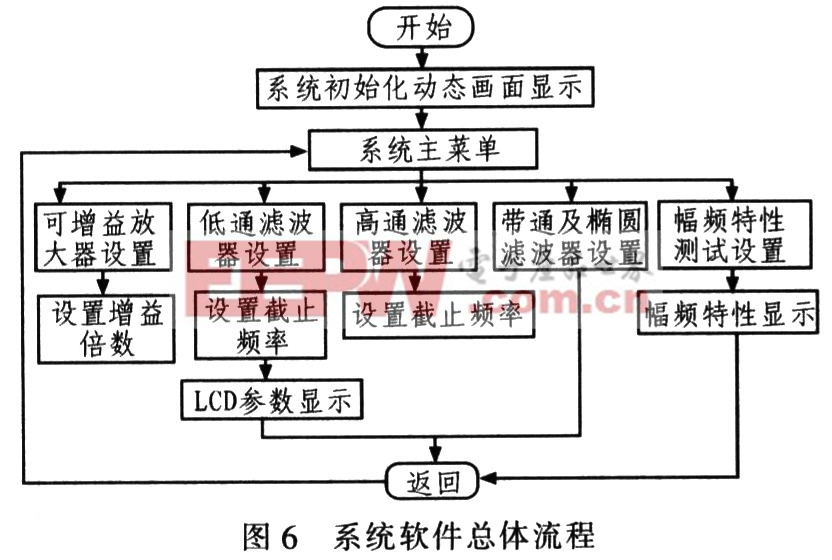

系统软件设计主要有3部分:(1)设置放大器的增益,控制高低通等滤波器的切换并设定其截止频率;(2)幅频特性测试.产生DDS信号的频率控制字,控制频率步进,测量并显示信号通过滤波器后的幅值信息;(3)人机交互功能。系统软件设计采用模块化思想,模块内部采用层次化设计,将硬件接口处理及初始化部分作为底层的子程序,控制硬件接口的中断并向上层提供接口读取数据;中间层程序完成底层数据的收集和处理,将其结果上传至最终的上层功能控制程序;最后主程序通过调用相关的功能控制模块实现对整个系统的构建。系统软件总体流程如图6所示。

5 测试结果

(1)用信号源在放大器输入端输入峰值为10 mV的正弦信号,在100 Hz~40 kHz范围内,用双踪示波器检测放大器的通频带。预置放大器增益,用低频毫伏表测试输出信号的有效值并检测其实际增益,计算增益误差,检验增益步进。测试结果表明放大器的增益范围为0~60 dB,步进为10 dB,增益误差小于0.5%。

评论