ADC输入噪声利弊分析

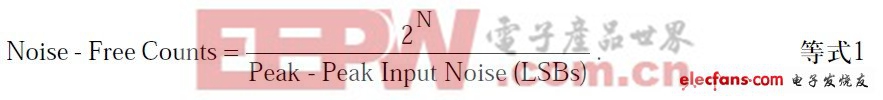

ADC的无噪声代码分辨率是指这样一个位数,如果超过该位数,则无法明确无误地解析各个代码,原因是存在所有ADC都具有的有效输入噪声(或折合到输入端噪声),如上文所述。该噪声可以表示为均方根量,单位通常是LSB rms.乘以系数6.6可以将均方根噪声转换为峰峰值噪声(用LSB峰峰值表示)。N位ADC的总范围为2NLSB.因此,无噪声采样总数等于:

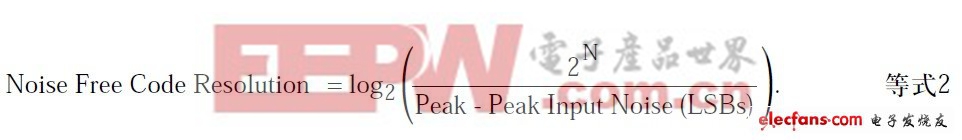

对无噪声采样数求以2为底的对数可以得到无噪声代码分辨率:

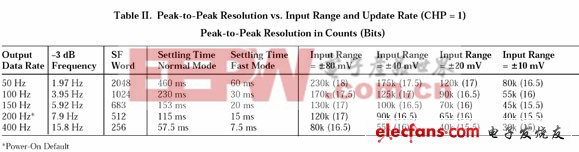

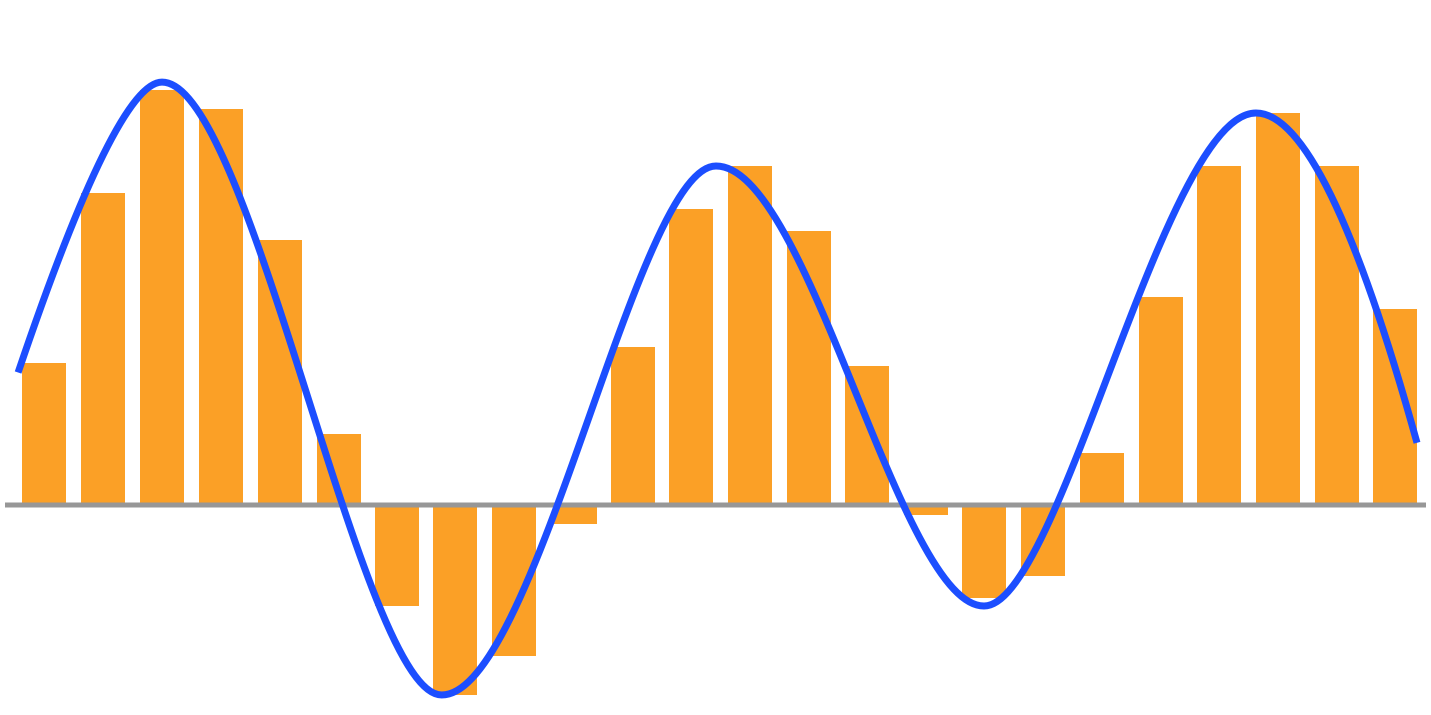

无噪声代码分辨率规格一般与高分辨率 - 型测量ADC相关,通常是采样速率、数字滤波器带宽和可编程增益放大器(PGA)增益的函数。图4所示为从 - 型测量ADC AD7730获得的一个典型数据表。

图4:Σ-Δ型ADC AD7730的无噪声代码分辨率

注意,当输出数据速率为50 Hz、输入范围为±10 mV时,无噪声代码分辨率为16.5位(80,000无噪声采样)。这些条件下的建立时间为460 ms,因此该ADC是精密电子秤应用的理想之选。对于适合精密测量应用的高分辨率 - 型ADC,大部分数据手册都提供了类似的数据。

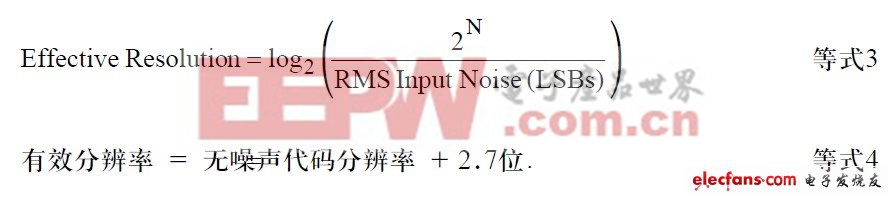

有时候会利用满量程范围与均方根输入噪声(而非峰峰值噪声)的比值来计算分辨率,该分辨率称为有效分辨率.注意:在相同条件下,有效分辨率比无噪声代码分辨率高log2(6.6),约2.7位。

有些制造商更愿意规定有效分辨率,而不是无噪声代码分辨率,因为前者的位数较高。用户应仔细检查数据手册,弄清它到底指定哪一种分辨率。

通过数字均值法提高ADC分辨率并降低噪声

折合到输入端噪声的影响可以通过数字均值方法降低。假设一个16位ADC具有15位无噪声分辨率,采样速率为100 kSPS.对于每个输出样本,如果对两个样本进行平均,则有效采样速率降至50 kSPS,SNR提高3 dB,无噪声位数提高到15.5位。如果对四个样本进行平均,则采样速率降至25 kSPS,SNR提高6 dB,无噪声位数提高到16位。

事实上,如果对16个样本进行平均,则输出采样速率降至6.25 kSPS,SNR再提高6 dB,无噪声位数提高到17位。为了利用额外的分辨率,均值算法必须在较大的有效位数上执行。

均值过程还有助于消除ADC传递函数的DNL误差,这可以通过下面的简单例子来说明:假设ADC在量化电平k处有一个失码,虽然代码k由于DNL误差较大而丢失,但两个相邻代码k – 1和k + 1的平均值等于k.

因此,可以利用该技术来有效提高ADC的动态范围,代价是整体输出采样速率降低并且需要额外的数字硬件。不过应注意,均值并不能校正ADC固有的积分非线性。

现在考虑这样一种情况:ADC的折合到输入端噪声非常低,直方图总是显示一个明确的代码,对于这种ADC,数字均值有何作用呢?答案很简单--没有作用!无论对多少样本进行平均,答案始终相同。但只要将足够大的噪声增加到输入信号中,使得直方图中有一个以上的代码,那么均值方法又会发挥效用。因此,少量噪声可能是好事情(至少对于均值方法而言),但输入端存在的噪声越高,为实现相同分辨率所需的均值样本数越多。

切勿将有效位数(ENOB)与有效分辨率或无噪声代码分辨率混为一谈

由于这些术语名称相似,有效位数和有效分辨率常被误认为是一回事,事实并非如此。

有效位数(ENOB)来自对ADC输出的FFT分析,条件是用一个满量程正弦波输入信号激励ADC.计算所有噪声和失真项的和方根(RSS)值,信号对噪声和失真的比值定义为信纳比SINAD或S/(N+D)。理想N位ADC的理论SNR为:

将计算所得的SINAD值替换等式5中的SNR,并求解N,便得到ENOB:

用于计算SINAD和ENOB的噪声和失真不仅包括折合到输入端噪声,而且包括量化噪声和失真项。SINAD和ENOB用于衡量ADC的动态性能,有效分辨率和无噪声代码分辨率则用于衡量ADC在无量化噪声的直流输入条件下的噪声。

评论