Xilinx FPGA的功耗优化设计

降低静态功率的另一个方法是仔细审查设计,避免冗余的直流消耗源。设计中经常会使用到具有多余或隐藏DCM或PLL的模块,这种情况可能在模块设计后忘记将多余的资源去除,或者在构建下一代产品时使用了一些遗留代码。将DCM或PLL抽象到设计的顶层,这样模块之间就可以共享资源,从而可进一步减小设计的规模并降低直流功率。

更好地使用存储器模块也可帮助降低FPGA设计的动态功耗,从而进一步降低总体功耗。由于动态功耗是容抗(面积或长度)和频率的函数,因此应当检查设计中访问块存储器的方式并确定能够对容抗和频率进行优化的区域。

Xilinx FPGA提供两种类型的存储器阵列。18Kbit或36Kbit的BRAM是针对大存储器模块而优化的。LUTRAM基于FPGA中的查找表,是针对细粒度存储而优化的。Xilinx Virtex-5 FPGA中,LUTRAM的单位是64bit。

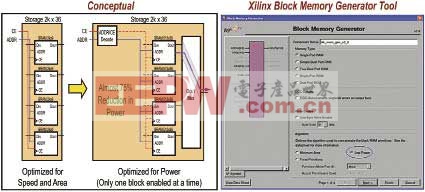

在这两种类型中,BRAM通常功耗要大一些。启用后的BRAM静态功率是其功耗的最大部分,跳变带来的功耗居于第二位。设计人员可以采取一些步骤来优化BRAM的功耗。例如,可以仅在读或写周期才启用BRAM。对于较小的存储器模块可以使用LUTRAM来代替BRAM,将BRAM留给较大的存储器模块使用。此外,还可以尝试将BRAM用于多个大型模块。另一种技术是合理安排存储器阵列来减少其占用的延迟面积、使性能最大化并尽量降低其功耗。图1左侧给出了一个针对速度和面积而优化的2K x 36bit存储阵列。

我们利用四个2K x 9bit模块并行构成这一存储阵列,并在需要新值时启用(Enable)所有四个模块。另一方法是采用四个512 x 36bit模块来安排2K x 36bit,但利用低两位地址解码来选择访问哪个512 x 36bit模块。在后一种情况下,某个时间仅访问一个存储器块,功耗将比第一种方法降低75%。

图1右侧显示的是Xilinx公司的块存储器生成器(Block Memory Generator),利用它可以生成任意大小的存储器阵列并可以针对速度或功率对其进行优化。图2则给出了具体应用中的Xilinx Power Estimator,比较了在给定的使能速率下N个模块同时启动与N/4模块启动时的功耗情况。结果显示动态功率降低了75%。

图1 速度和面积与功率优化存储器阵列(左)

以及Xilinx Block Memory Generator与功率面积选择(右)

Xilinx工具可帮助选择适合的存储器阵列。考虑某个设计中需要两组存储器区域。一种情况下需要运行在300MHz的16组64 x 32bit存储器结构(总位数为32K),另一种情况下需要16组512 x 36bit 存储器架构 (总位数为294K)。

看一下16组64 x 32bit存储器结构的功率比较,XPE工具显示出小存储器阵列最好用LUTRAM来实现,这样比用BRAM节约85%的功耗(如图3)。这是因为如果采用BRAM的话,只能用16个18K位的模块来实现16个极小(64 x 32bit)的存储器,有很多空间被浪费了。而第二种情况16组18K位阵列的功率比较,XPE显示情况正好相反,应当采用大一些的存储器阵列来实现(图4)。这种情况下,采用BRAM比采用LUTRAM可以节约28%的功耗,这是因为如果采用LUTRAM就需要启用更多的小粒度对象并增加更多的互连。

Xilinx FPGA的时钟门控功能

Xilinx FPGA的时钟门控功能提供了一些非常有意思的用途。例如,可以利用BUFGMUX时钟缓冲器将FPGA内的某个全局时钟关闭,或者动态选择较慢的时钟。还可以使用BUFGCE时钟缓冲器进行按时钟周期(cycle-by-cycle)的门控,与ASIC设计中使用的时钟门控技术类似。设计中可以同时使用这两种功能。

评论