5.8GHz短距离无线收发系统的设计

2 数据链路控制

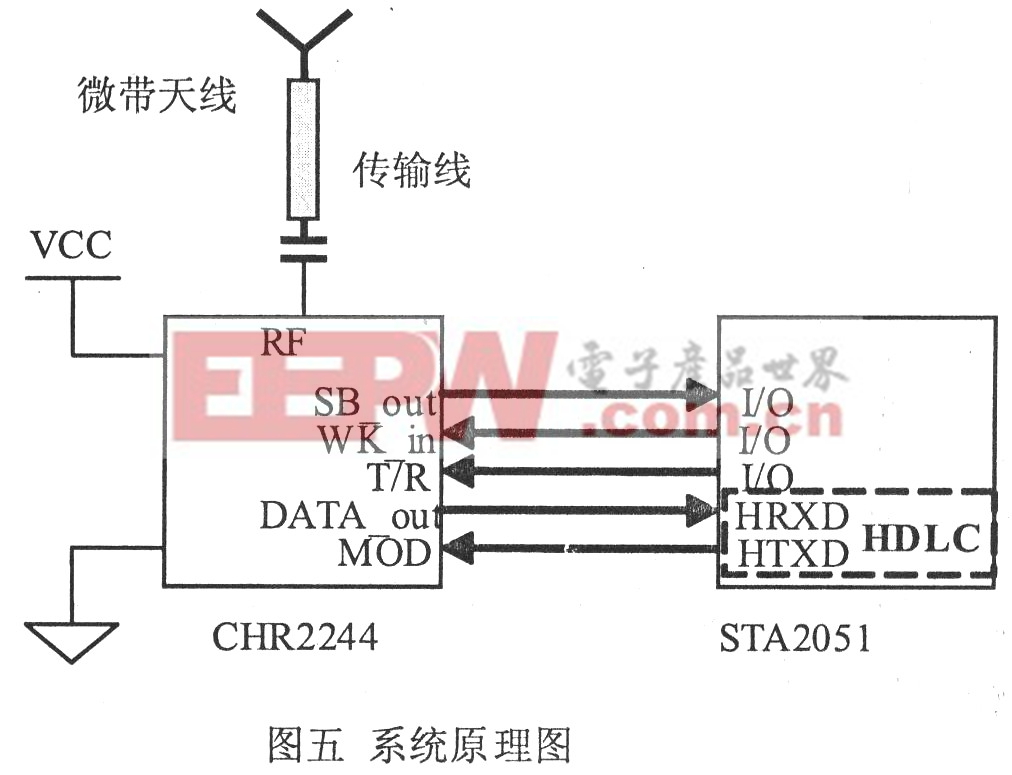

图五中,DATA_out和MOD端分别与处理器的高级数据链路控制器(HDLC)的传输数据输入端(HRXD)和传输数据输出端(HTXD)相连。HDLC主要有两部分组成:接收部分(HDLC接收器)和发送部分(HDLC发送器)。它在数据通信中将对数据链路层进行控制,包括标志检测和插入;零位检测和插入;帧校验序列产生和校验等。HDLC的帧格式如图六:

HDLC中设置数据编码格式为FMO;设上行链路数据传输速率是500kbps,下行为250kbps,HDLC设备所挂载的总线频率为32MHz,发送通道分频值为64,接收通道分频值为128。

HDLC的接收:HDLC将CHR2244传来的基带信号经FM0解码,根据前导码完成对数字信号0、1的同步,如果检测到帧开始和结束标志并且CRC正确,则把接收到的帧拷贝到接收缓冲区,然后产生接收中断通知CPU。

HDLC的发送:CPU把数据填充到HDLC的发送缓冲区后,启动HDLC发送。HDLC对数据进行零位插入,添加帧标记.计算CRC,产生前导码和后导码,最后经FM0编码,通过HTXD递交给CHR2244,HDLC发送完毕后,产生发送中断通知CPU。

3 通信过程描述

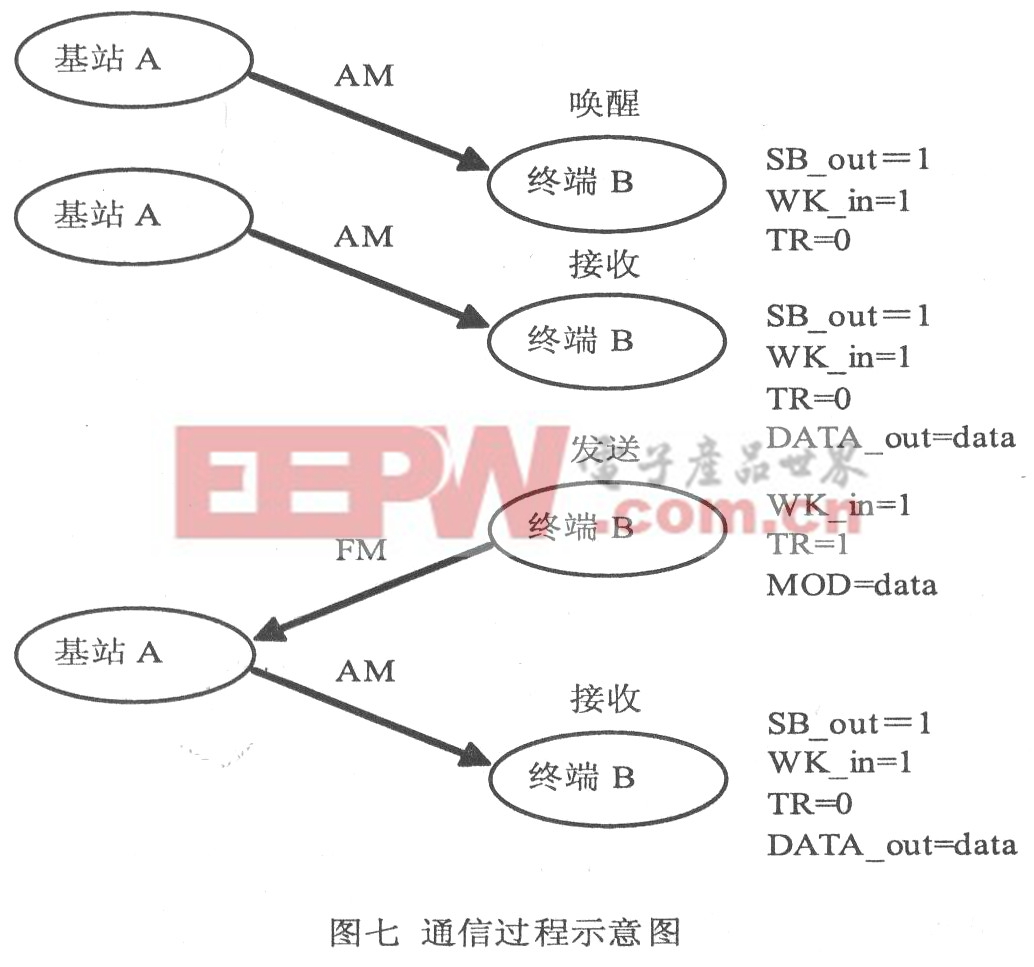

对系统进行短距离无线通信测试,整个通信过程如图七所示。描述如下:

一个已有收发系统作为基站A,本系统作为终端B。

1)初始状态WK_in=O,T/R=O,MOD=0。

2)基站A不发送信号。这时系统B的SB_out=0,WK_in=O,系统处于睡眠状态;

3)基站A以一定的时间间隔(如lOOms)重复发送一组250Kbps的5.8GHz AM信号。睡眠状态下B接收到A传来的AM信号,这时SB_out=1,CPU收到SB_out后,向WK_in输出高电平,唤醒B,并置TR=0,系统处于接收状态;接收状态下B接收A传来的AM信号,解调并由DATA_out输出。CPU收到数据后检查是否接收正确,如果接收正确,则准备向A反馈数据,这时置TR=l,系统处于发送状态。CPU将需要发送的数据通过MOD脚传输给CHR2244,在CHR2244内进行FSK调制后由天线发出传给基站A。数据发送完成后,CPU置TR=O,系统重新切换到接收状态。

4)基站A收到来自B的数据,检查是否正确,正确则表明通信成功。完成一次双向通信。

4 总结

系统按照3中所述进行室内测试,测试结果表明上下链路均能正常工作,可以完成短距离数据交互。若在此基础上进行一些改进优化和应用程序的开发,系统将有望运用在一些实际的短距离无线通信领域中。

评论