跳频收发系统中的跳频频率合成器设计

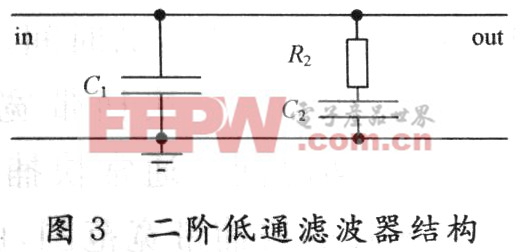

AD9850是采用并行传输方式从计算机接收频率和相位控制字的,这是因为考虑到并行方式传输的速度比串行方式快。总共40位控制字,通过8位数据总线送到AD9850的输入寄存器中,需重复5次。在FQUD信号上升沿调入40位控制字,同时把地址指针复位到第一个寄存器。接着在W_CLK信号的上升沿到来时,把最高的8位数据装入第一个寄存器,并把地址指针指向下一个寄存器。这样,连续5个W_CLK上升沿后,就把40位控制字都装入了寄存器,W_CLK信号不再起作用,直到收到复位信号或FQ_UD信号的上升沿时,才重新开始新一轮的数据装入。鉴相器LMX2306本身就带有一个前置双模分频器(8/9分频)和两个可编程分频器N,R,采用串行输入的方式。在初始化时只要给N寄存器、R寄存器和F功能寄存器输入正确的数据,就可以正常工作了。LMX2306的外部环路滤波器在锁相环路中起非常重要的作用,环路滤波器形式和参数的选取是锁相环设计与调试的关键,在很大程度上决了定环路的噪声、捕获和跟踪性能等。该环路滤波器选用二阶无源比例积分滤波器,其二阶低通滤波器结构如图3所示。本文引用地址:http://www.eepw.com.cn/article/157987.htm

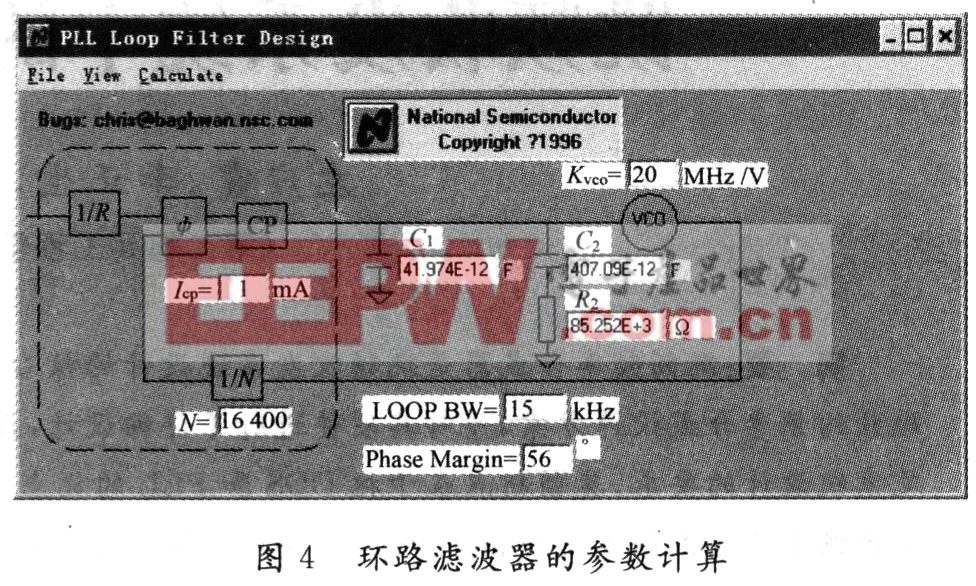

利用美国国半公司提供的PLL环路滤波器设计软件Loopfilt可方便地计算出滤波器的参数,如图4所示。

在实际电路中,环路滤波器的参数选定为:

![]()

2 跳频频率合成器的性能估算

在分析跳频频率合成器的性能时,尤其对于快速跳频系统来说,频率分辨率和换频性能是其中两个很重要的指标。

在该方案中,跳频频率合成器是由DDS激励PLL组成的。因DDS的系统时钟为96 MHz,则AD9850的输出频率fDDS=96 MHz/232△0.022 35 Hz。锁相环PLL的输出频率为:

![]()

式中:Ntotal为环路总的分频比。设计中要使最后的输出频率fo在410~468 MHz内跳变,频道间隔为25 kHz。由相关参考文献中的公式可算得:R=400 Ω,Ntotal=16 400,即B=2 050,A=0,则编程使fDDS在10~11.414 346 MHz内变化,那么fo将在410~468 MHz内跳变,其频率分辨率(单位Hz)为:

![]()

该跳频频率合成器总的跳频转换时间也应该是这两部分跳频转换时间之和。DDS的换频时间很短,对AD9850来说,是ns级的,几乎可以忽略不计。所以整个跳频频率合成器的跳频转换时间主要由PLL的跳频转换时间决定。

在工程上,PLL的跳频转换时间可以用PLL环路的最大快捕时间TLmax做估算:

![]()

设计中,ωn=15 000×2π;工程上ξ=0.707,则TLmax△75μs。所以,频率建立时间TPLL=75μs,跳频周期可为750μs,跳频速率最高可达1 333跳/s,满足系统设计的1 000跳/s的要求。

3 结语

跳频频率合成器是跳频收发系统设计的核心,也是技术实现的一个难点。设计中把DDS和PLL的优点有机地结合起来实现了高速跳频,摒弃了用直接数字频率合成DDS输出频率不能太高或用锁相环PLL合成频率锁定时间较长的缺点,满足了系统设计的要求。

评论