波特率连续可调的串口通信技术

其中,Mode为循环相位累加器的最大值,即模值,可以预先设定。N为一个周期所包含的采样点数。Mode,N的取值要综合考虑fclk和FCW的值,以获得一个随FCW线性变化的fclk即实现了fclk随FCW变化而变化的连续可调。

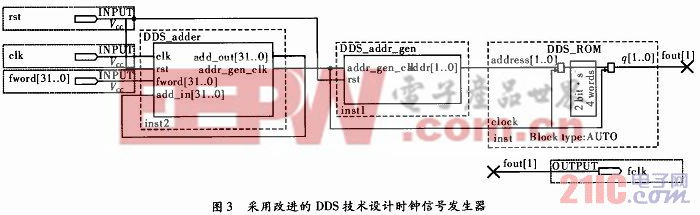

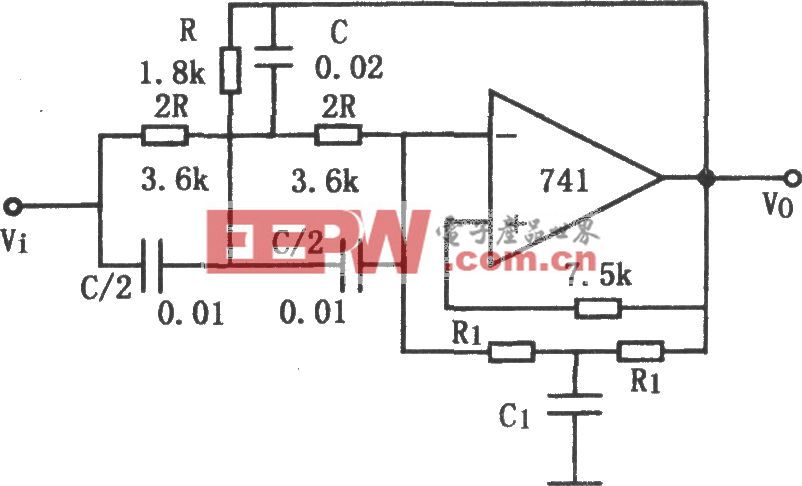

1.2.4 采用的DDS技术

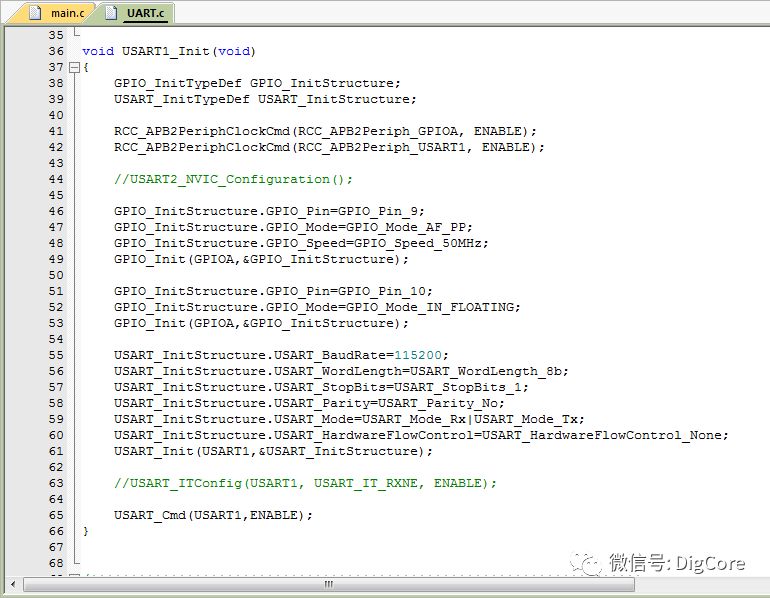

针对RS232标准中串行通信中波特率的一般要求范围300~115 200 bit·s-1,采用改进的DDS技术,基于FPGA,设计如图3所示的DDS模块。本文引用地址:http://www.eepw.com.cn/article/155189.htm

其中的循环相位累加器模块DDS_adder模块,相位寄存器模块DDS_addr_gen是基于硬件描述语言设计的模块,ROM模块DDS_ROM是基于FPGA的宏模块。

在本设计中实现发送时钟fclk在300~115 200 bit·s-1范围内步进为0.1 bit·s-1的调节。其中,Mode取7 812 500,N取4,fclk为外部晶振提供的频率为50 MHz时钟。

因此,有△F=1.6 FCW。其中,FCW为应用程序所传送的实际控制频率的10倍,根据UART协议,发送时钟的频率至少是串口通信波特率的16倍。所以,以上的参数设置即实现了步进为0.1 bit·s-1的连续可调的波特率设置。

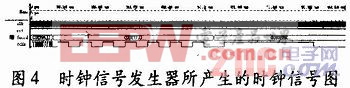

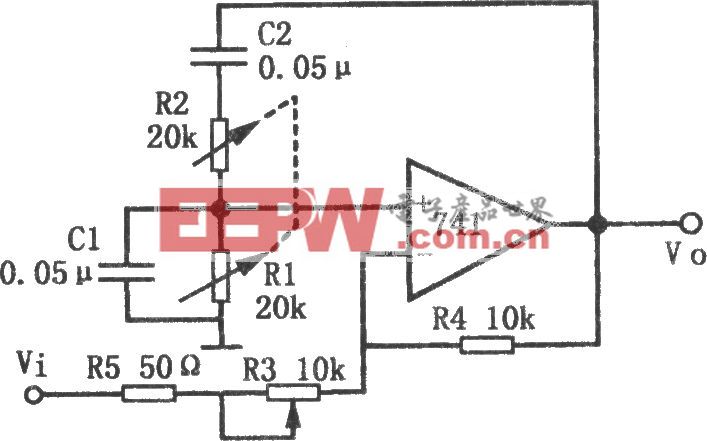

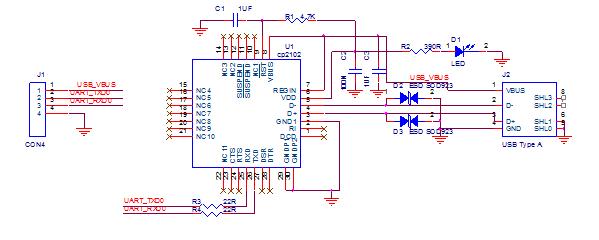

1.2.5 连续可调信号的验证

文中DDS技术是基于FPGA实现的。根据不同的频率控制字fword输入,经过几个过渡时钟后,DDS模块即可以稳定产生随频率变化的时钟信号fclk。

在图4的仿真中,所仿真的频率点是115 200 Hz,9 600 Hz,1 200 Hz,,对应的fword为0x00119400,0x00017700,0x00002EE0。

评论