便携式高速数据采集系统设计

2 AD1671控制及采集系统工作原理

图3是AD1671的AD转换时序图。

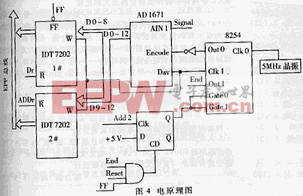

AD1671在Encode信号上升沿开始A/D转换,Dav信号在本次转换完成前一定时间变低,直到Dav出现上升沿表示本次转换结束。为防止数字噪声耦合带来的误差,Encode信号应在Dav信号变低后50ns内变低。系统中通过8254计数器对晶振进行分频来给AD1671提供Encode信号,以满足其工作时序的需要。系统原理图如图4所示。系统初始化时,向8254的Clock0写入计数值,由此可以灵活改变采样间隔,同时写入Clock1的计数值用来控制采样的个数。晶振采用5MHz有源四脚晶振,D触发器实现触发功能,系统工作原理如下:

AD1671在Encode信号上升沿开始A/D转换,Dav信号在本次转换完成前一定时间变低,直到Dav出现上升沿表示本次转换结束。为防止数字噪声耦合带来的误差,Encode信号应在Dav信号变低后50ns内变低。系统中通过8254计数器对晶振进行分频来给AD1671提供Encode信号,以满足其工作时序的需要。系统原理图如图4所示。系统初始化时,向8254的Clock0写入计数值,由此可以灵活改变采样间隔,同时写入Clock1的计数值用来控制采样的个数。晶振采用5MHz有源四脚晶振,D触发器实现触发功能,系统工作原理如下:

系统初始化完成后,经地址译码器产生Add2信号,使D触发器状态翻转,由低变到高,8254计数使能端Gate0、Gate1变高,8254开始方式2的计数。当Clock0的计数时间到时,发出一个宽度为一时钟周期的负脉冲,经反向送入Encode,启动AD1671进行A/D转换。一次转换结束,利用Dav信号将转换的数据写入IDT7202,同时Clock1计数一次。当Clock1计数时间到后,发出一个脉冲,用来实现对D触发器的清零,使Gate0、Gate1变低,停止AD1671转换,完成一次系统的采集工作。

3 FIFO与EPP的接口电路

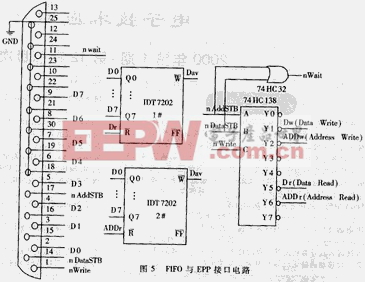

图5是EPP与IDT7202的接口电路。

此电路是基于EPP1.9设计的。nDataSTB与nAddSTB组合产生nWait回送信号,实现连锁握手。方案中分别用数据读周期、地址读周期对1#FIFO、2#FIFO进行读取。EPP模式设定后,对FIFO存储器的读取非常简单。通过产生一个单I/O读指令到“基址+4”,EPP控制器就会产生所需的选通信号,用EPP数据读周期传送数据。对“基址+3”的I/O操作,可产生地址周期信号。

此电路是基于EPP1.9设计的。nDataSTB与nAddSTB组合产生nWait回送信号,实现连锁握手。方案中分别用数据读周期、地址读周期对1#FIFO、2#FIFO进行读取。EPP模式设定后,对FIFO存储器的读取非常简单。通过产生一个单I/O读指令到“基址+4”,EPP控制器就会产生所需的选通信号,用EPP数据读周期传送数据。对“基址+3”的I/O操作,可产生地址周期信号。

C语言指令如下:

读一个字节数据:Data=Inportb(Base_Addr+4);

读一个字节地址: Data=Inportb(Base_Addr+3);

实际应用中FIFO的存取时间达到ns 级,EPP的速度也接近ISA总线的速率。上述接口电路属于高频,电路设计要注意消除干扰。FIFO的读写信源应尽量靠近FIFO,没用到的数据输入端应接地或VCC等。

评论