256 级灰度显示 - 基于FPGA的OLED真彩色显示设计

所谓图像的灰度等级就是指图像亮度深浅的层次,将基色的发光亮度按强度大小划分,就是灰度级。

显示屏能产生的灰度级越高,显示的颜色和图像层次就越多。而且人的视觉系统对亮度强弱的感受不仅与亮度本身的强弱相关,还与发光时间和点亮面积有关,在一定时间范围内,点亮时问越长、面积越大,人眼感觉的发光强度就越强。因而利用人眼对快速的亮暗闪烁并不敏感的“暂留”效应,变换发光体的点亮时间和面积来区分亮度,就会形成一种不同灰度级画面的视觉,一般灰度级越高,所显示的颜色和图像层次就越多,图像越柔和,图像层次越逼真。高灰度级以及有效的灰度调制方式对高清晰度显示的发展极其重要,目前OLED 显示驱动一个亟需解决的是灰度的精确性问题。

OLED 显示屏是可以用传统的模拟电压控制法来实现灰度,问题在于: 亮度和数据电压之间呈非线性关系,缺少一个渐变的易于控制的线性区间,因此,采用模拟电压法调节发光强度,难以精确、有效地实现OLED 的灰度级显示,现在总的趋势是使用数字驱动电路。

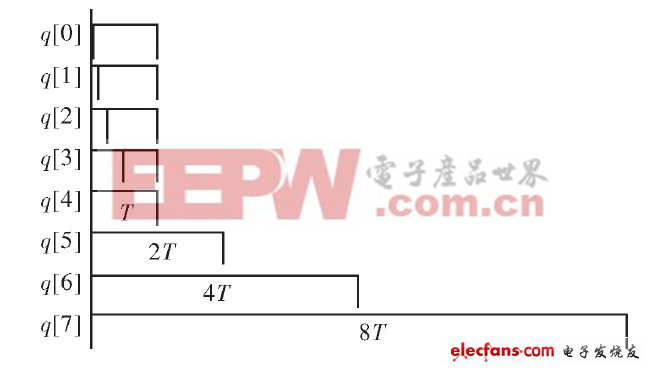

图2 分时显示示意图。

数字驱动电路的困难在于工作频率比模拟驱动电路高得多,现阶段较为实用的灰度调制方法主要有两种。一种是脉宽调制法,即对驱动脉冲实现占空比的控制; 另一种方法是子场控制法,这种方法将发光时间按1∶ 2∶ 4∶ 8∶ …划分为若干个子场,不同的子场导通组合,就能实现不同的灰度等级。但采用脉宽调制法,其时序复杂,要求显示屏有较高响应速度; 而采用子场法要求驱动频率较高,对高灰度级的实现难度大。

考虑到帧频与OLED 屏体显示效率的折中,使驱动电路工作频率在一个合理水平,在脉宽调制和子场原理的基础上,对这两种方法进行优化,256 级灰度采用通过对图像数据按位分时显示的方法实现,即对输入的8 bit 像素信号RGB,通过给每种颜色字节的不同位分配不同的显示时间达到灰度显示的目的,使每位的显示时间为128∶ 64∶ 32∶ 16∶ 8∶ 4∶ 2∶ 1,利用其组合可以得到256 级灰度显示所对应的子像素发光时间,实现视觉上的256 级灰度即1 667 万色显示,以实现高质量的显示画面。

为实现256 级灰度,将一个像素点的扫描时间分成19 个单位时间t,8 bit 灰度数据q[7: 0]从高位到低位所占的时间分别为8t,4t,2 t,t,t,t,t,t.为使不同位显示时间成一定比例,从q[3]开始引入t /2 的消影时间,q[2]引入t /4 的消影时间,d[1]引入t /8 的消影时间,d[0]引入t /16 的消影时间,如图2 所示,由控制电路产生消隐信号进行消隐。由此计算OLED 屏亮度百分比λ = ( 8 + 4 + 2 + l + 1 /2 + 1 /4 + 1 /8 + 1 /16 ) /19 = 83. 9%.

1. 3 FPGA 控制器

利用FPGA 的处理速度和数据宽度高的优势以及芯片中可利用的丰富资源,为分辨率为480 × RGB ×640 的OLED 显示屏设计了外围驱动控制电路。其主要作用是向OLED 显示屏提供扫描控制信号及进行OLED 显示数据的数字信号处理。

根据OLED 显示屏周边接口的结构和特性,利用FPGA 芯片为其设计外围的驱动控制系统,为OLED 屏提供控制信号以及传输所要显示的数据信号。

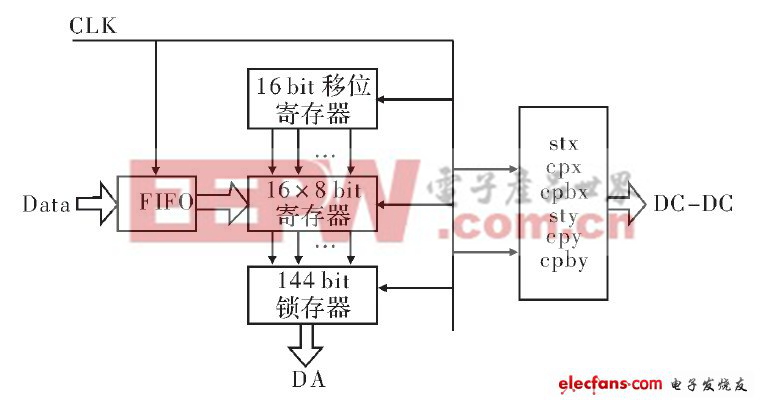

如图3 所示,经解码后的图像数据存入FIFO( First In First Out) 缓存中,在主时钟的控制下,FIFO中的图像数据将被载入到一个16 × 8 的数据装载寄存器,当这16 个8 位数据装载寄存器装满时,将被一个144 位的锁存器锁存,等待进入D/A 转换模块; 同时FPGA 控制器还将在主时钟的控制下产生行列移位时钟和行列扫描起始脉冲,产生的时钟和脉冲进入DC -DC 转换模块。

图3 FPGA 控制器结构框图。

1. 4 各种控制信号周期及频率

为使FPGA 控制器能工作于一个合理的驱动频率以及提高显示屏的亮度,在结构上采用标准单元块的形式。对于分辨率480 × 3 × 640 的显示屏,以8 × 16个显示像素灯管构成一个单元块,将480 × 3 行分组组合成为90 个块( Block) ,即每块由一组列信号同时驱动16 行像素。设计列扫描驱动电路时,将640 列电极分组组合成为80 个块( Block) ,每个块并行驱动8 列像素。

OLED 显示屏的刷新频率是60 Hz /s,即显示一帧图像的时间为1 /60 s,设为T,所以,行扫描起始信号stx 的周期T 为16 667 μs,占空比为1∶ 90; 因为OLED显示屏480 × 3 行电极分组组合成为90 个Block,所以每一块的选通时间为T /90,即185. 185 μs.而cpx 和cpbx 是一对反相不交叠的脉冲信号,占空比为50%,在脉冲信号的高电平和低电平时,都有一个Block 行像素被选通,即在cpx 和cpbx 一个周期内有两个Block 行像素被选通,所以行扫描驱动脉冲cpx 和cpbx的周期为T /45,即370. 370 μs.

同理,OLED 显示屏的列被分为80 个Block,每个列Block 的选通时间为2. 315 μs,列扫描起始信号sty的周期为185. 185 μs,占空比为1 ∶ 80.列驱动脉冲cpy 和cpby 亦是一对反相不交叠的脉冲信号,占空比为50%,在脉冲信号的高电平和低电平时,都有一个Block 被选通。由于每个列Block 的选通时间为2. 315 μs,所以列扫描驱动脉冲cpy 和cpby 的周期为4. 630 μs.

在每个列Block 选通期间,从FIFO 中并行读出的8 个8 bit 数据进入数据锁存器锁存。在每个BLOCK选通期间都将进行一次数据的锁存,所以数据锁存信号Lock 的周期为2. 315 μs.因为当16 个8 位的数据装载寄存器都载满数据的时候才进行这144 个数据的锁存,所以16 位移位寄存器时钟clk _reg 的周期为0. 145 μs.从FIFO 中读出数据的速度必须和向数据装载寄存器中装载数据的速度一致,则FIFO 的读时钟clk _ fifo 的周期也为0. 145 μs.对0. 15 μs( 6. 896 MHz) 进行近似为7 MHz,所以令系统的基本时钟为14 MHz,由FPGA 外部晶振产生。读时钟为基本时钟的二分频。

评论