基于DSP+FPGA的磁铁电源控制器的设计

2.4 驱动电路的设计

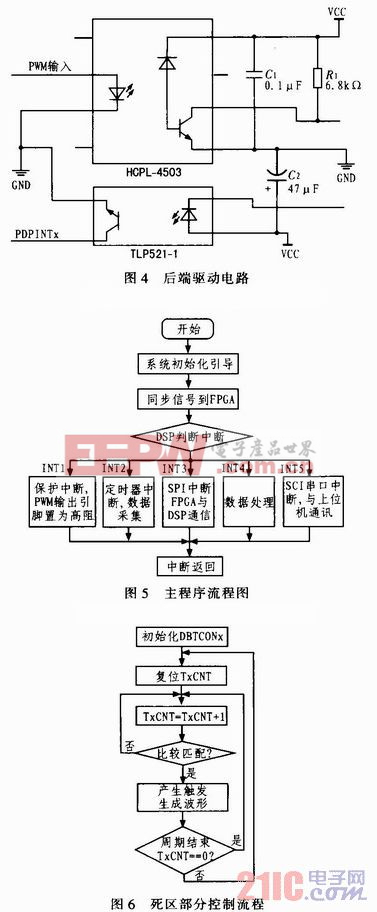

图4的驱动电路中高速光耦HCPL-4503快速实现信号的转换和隔离,而故障信号经低速光耦TLP521-1隔离后送至PDPINTx引脚,PWM输出引脚变为高阻态,同时产生一个中断,封锁驱动信号,关闭功率开关管。本文引用地址:http://www.eepw.com.cn/article/148555.htm

3 控制器软件设计

当发生中断时,DSP的CPU会根据中断响应的优先级和中断向量表判断,跳至相应的子程序执行,实现各自的功能。图5为主程序的流程图。

为防止上下两桥臂开关器件同时导通,驱动波形需要具有一定的死区时间。设置DSP死区控制寄存器DBTCONx[8-11]位死区定时器周期为m,DBTCON位的死区定时器预定标因子为x/p,若通用定时器时钟周期为t,则死区时间ts=m*p*t。死区部分控制流程如图6所示。

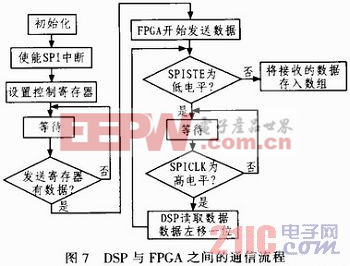

图7为DSP和FPGA之间的通信流程。波特率的配置通过对DSP的SPIBRR寄存器的编程实现,在SPI接口设计时应注意使用系统时钟对SCLK信号进行同步以减少SCLK引起的通信错误。

4 结束语

采用DSP+FPGA架构的磁铁电源控制器兼有两种信号处理芯片的优越性,有效的提高了运算速度和精度。在后续的研究中根据需要设置相应参数,选择合适的控制算法,以满足磁铁电源输出极低纹波和受精确控制的电流。

评论