- 1 引言 锁相环(PLL)是一个能够跟踪输入信号相位的闭环自动控制系统,它由鉴相器(PD)、环路滤波器(LF)、压 ...

- 关键字:

锁相环 YTO 自校准

- Hittite 微波公司是在通信及军事市场拥有完整的MMIC解决方案的世界级供应商。该公司最近拓展了其领先业界的锁相环产品线,推出高精度宽带锁相环芯片HMC830LP6GE,工作频率为25MHz—3000MHz,覆盖所有常用的通信频段。

产品简介

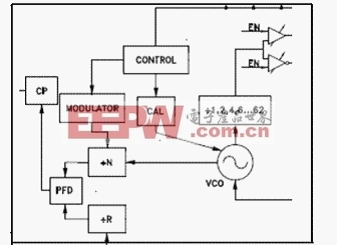

HMC830LP6GE是内部集成了VCO的小数分频锁相环芯片,以及可工作在100MHz的相位检测器和delta-sigma调制器,这使的其在较宽的环路带宽内有着极好的频谱特性。

性能特征与使用

HMC830LP6GE的

- 关键字:

Hittite 锁相环 HMC830LP6GE

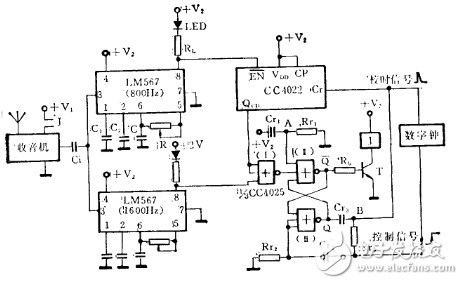

- 在电机转速控制系统中,经常需要对电机的转速信号进行测量和处理,以达到精确控制转速的目的。通常采用旋转编码...

- 关键字:

转速控制 窄带跟踪滤波 锁相环

- 摘要:利用锁相环进行载波跟踪是获取本地载波的一种重要方法,针对锁相环的噪声性能和跟踪速度不能同时达到最优的限制,在锁相环PLL中引入自适应模块,根据环路所处的环境自适应对PLL环路参数做出调整。设计中利用仿

- 关键字:

FPGA 锁相环

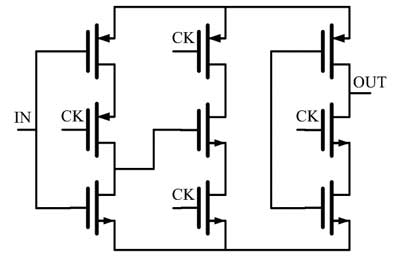

- 一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。本文给出了一种基于fpga的数字锁相环位同步提取电路。

- 关键字:

FPGA 锁相环 电路设计 位同步

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

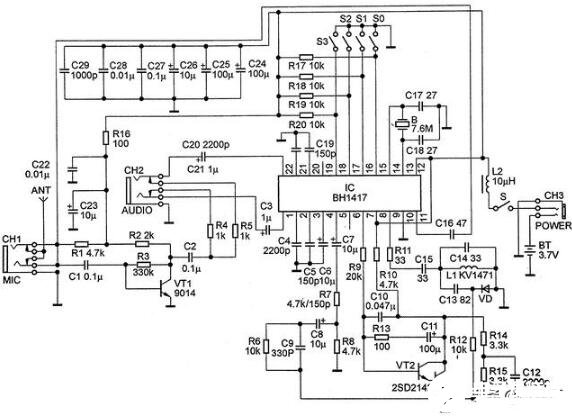

- 关键字:

AD9898 UHF波段 频率合成器 锁相环

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

跳频通信 信号源 DDS+PLL 锁相环

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

频率合成器 仿真 锁相环 微卫星系统

- 图3.24给出了CADILLAC时钟相位调整电路的框图。对于大规模生产测试,可能值得构造这样的电路。对于普通的实验测试,则太麻烦了。电路将总线时钟进行N分频,然后通过一个-频率比较器把它与一个同样经过N分频的本地振荡

- 关键字:

锁相环 时间调整

- 电路的功能很多电路都要求把频率准确地倍增,使用PLL电路可很容易组成满足这种要求的电路。例如主振频率为1KHZ,若使用倍增器内插10个脉冲,可变成10KHZ的脉冲信号。在VCO中,即使主振频率发生变化,也能获得跟踪主振

- 关键字:

PLL 10 IC的 锁相环

- 摘要:延时锁相环(DLL)是一种基于数字电路实现的时钟管理技术。DLL可用以消除时钟偏斜,对输入时钟进行分频、倍频、移相等操作。文中介绍了FPGA芯片内DLL的结构和设计方案,在其基础上提出可实现快速锁定的延时锁相环

- 关键字:

FPGA 延时 锁相环

- 摘要:叙述了全数字锁相环的工作原理,提出了应用VHDL 技术设计全数字锁相环的方法,并用复杂可编程逻辑器件CPLD 予以实现,给出了系统主要模块的设计过程和仿真结果。0 引言全数字锁相环(DPLL) 由于避免了模拟锁相环存

- 关键字:

VHDL 全数字 电路设计 锁相环

锁相环介绍

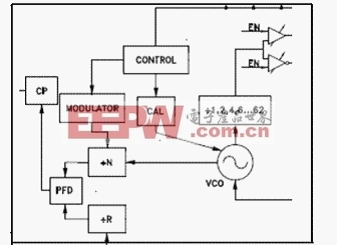

能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。锁相环的基本结构如图1,其中鉴相器用来鉴别输入信号ui与输出信号u0之间的相位差,并输出误差电压ud。ud中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压uC。uC作用于压控振荡器的结果是把它的输出振荡频率f0拉向环路输入信号频率fi,当二者相等时,环路被锁定,称为入锁。维持锁定的直流控制电压由鉴相器 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473