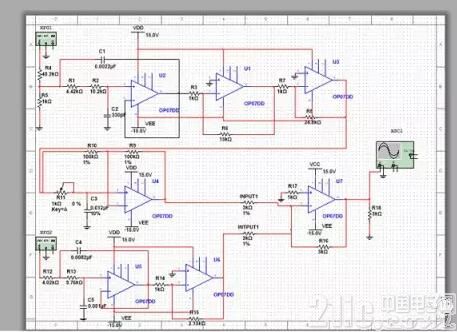

- 你了解如何如何分析组合逻辑电路与时序逻辑电路吗? 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。 逻辑电路的特点 组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。 而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。 很多人往往对于这两种逻辑电路的分析有困惑。 组合逻辑电路 组合逻辑电路中,

- 关键字:

组合逻辑电路 时序逻辑电路

- 组合逻辑电路特点

①组合电路是由逻辑门(表示的数字器件)和电子元件组成的电路,电路中没有反馈,没有记忆元件;

②组合电路任一时刻的输出状态仅取决于该时刻各输入的状态组合,而与时间变量无关。

组合逻辑电路结构

组合逻辑电路: 任一时刻的输出状态仅取决于该时刻各输入状态组合的数字电路。

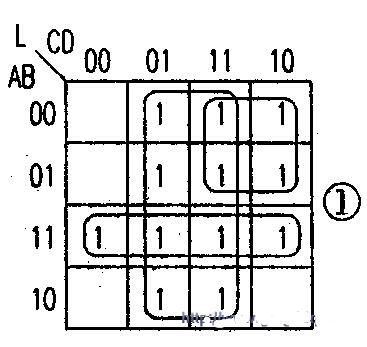

由真值表知,电路将输入二进制码A3A2A1 转换输出循环码Y3 Y2 Y1。即任何时刻,输入一组二进制码,输出便是该组码对应的循环码,而与时间变量无关。

- 关键字:

组合逻辑电路

- 数字逻辑电路分为两种,分别是组合逻辑与时序逻辑。(1)组合逻辑:输出只是当前输入逻辑电平的函数(有延时),与电路的原始状态无关的逻辑电路。也就是说,当输入信号中的任何一个发生变化时,输出都有可能会根据其变化

- 关键字:

Verilog HDL 基础教程 组合逻辑电路

- 1.组合逻辑电路的特点

若在一个数字电路中,电路的任一时刻的输出,仅仅决定于该时刻电路的输入,而与电路原来的状态无关,则次电路就称为组合逻辑电路,简称组合电路。若组合逻辑电路只有一个输出量,称为单输出组合逻辑电路;若有一个以上输出量,称为多输出组合逻辑电路。

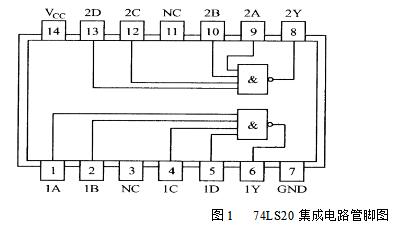

2.组合逻辑电路的组成

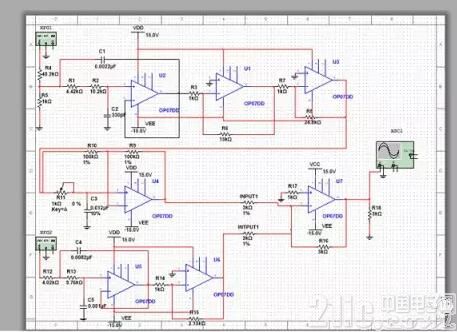

组合逻辑电路的组成方框图如图1所示。它有n个输入端,m个输出端,Xi为输入逻辑变量,Yi为输出逻辑变量。输出变量Y1,Y2,...,Ym是输入变量X1、X2,…,Xn的函数,即:

&nb

- 关键字:

组合逻辑电路 逻辑电路

组合逻辑电路介绍

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473