随着大模型、高性能计算、量化交易和自动驾驶等大数据量和低延迟计算场景不断涌现,加速数据处理的需求日益增长,对计算器件和硬件平台提出的要求也越来越高。发挥核心器件内部每一个计算单元的作用,以更大带宽连接内外部存储和周边计算以及网络资源,已经成为智能化技术的一个重要趋势。这使得片上网络(Network-on-Chip)这项已被提及多年,但工程上却不容易实现的技术再次受到关注。作为一种被广泛使用的硬件处理加速器,FPGA可以加速联网、运算和存储,其优点包括计算速度与ASIC相仿,也具备了高度的灵活性,能够为数据

关键字:

2D NoC FPGA

Sondrel 和业界领先的提供片上网络(NoC)互连和 IP部署软件以加快SoC创建的系统级芯片(SoC)系统IP供应商Arteris IP近日宣布, Sondrel 在其下一代先进驾驶辅助系统 (ADAS) 架构中采用 FlexNoC 互连 IP。选择Arteris IP 的片上互连是因为其可配置性和性能。该产品可满足 SFA 350A 多通道汽车 IP 平台的要求。FlexNoC 具有设计 NoC的能力,可以匹配 IP 模块的性能,以确保数据以正确的速度流入、流出和围绕SoC。它使设计人员能够在预算

关键字:

IP NOC

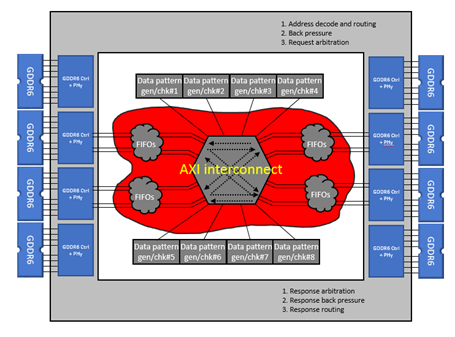

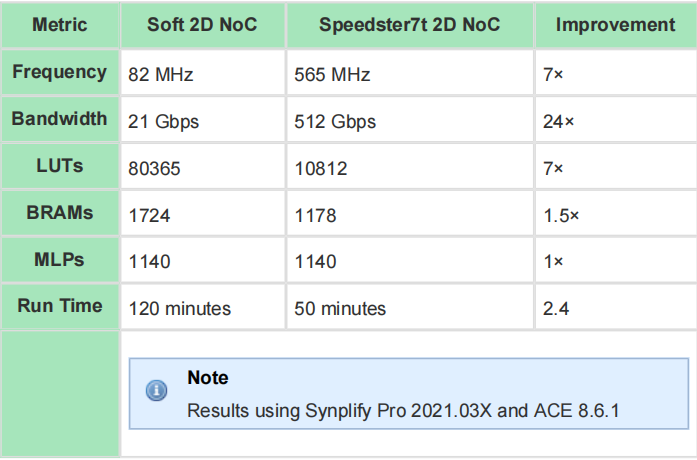

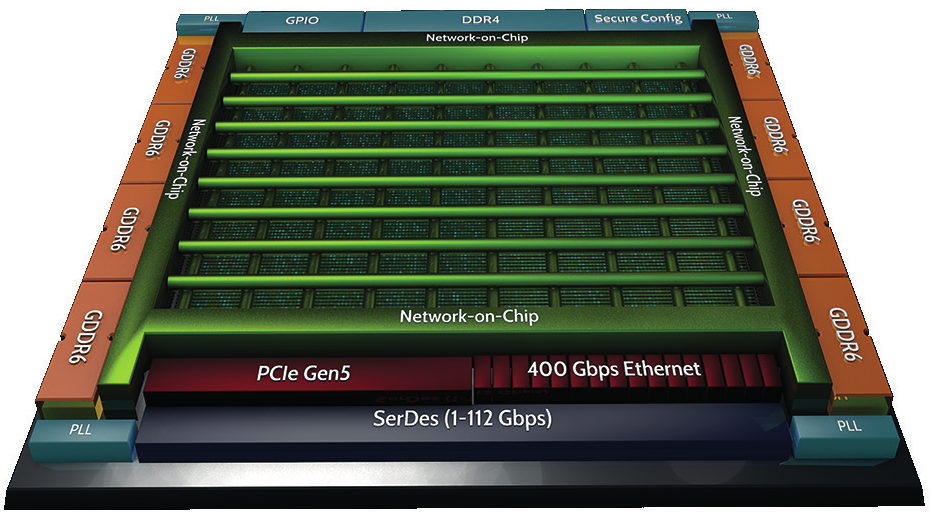

摘要随着旨在解决现代算法加速工作负载的设备越来越多,就必须能够在高速接口之间和整个器件中有效地移动高带宽数据流。Achronix的Speedster®7t独立FPGA芯片可以通过集成全新的、高度创新的二维片上网络(2D NoC)来处理这些高带宽数据流。Achronix的FPGA中特有的2D NoC实现是一种创新,它与用可编程逻辑资源来实现2D NoC的传统方法相比,有哪些创新和价值呢?本白皮书讨论了这两种实现2D NoC的方法,并提供了一个示例设计,以展示与软2D NoC实现相比,Achronix 2D

关键字:

Achronix FPGA 2D NoC

日益增长的数据加速需求对硬件平台提出了越来越高的要求,FPGA作为一种可编程可定制化的高性能硬件发挥着越来越重要的作用。近年来,高端FPGA芯片采用了越来越多的Hard IP去提升FPGA外围的数据传输带宽以及存储器带宽。但是在FPGA内部,可编程逻辑部分随着工艺提升而不断进步的同时,内外部数据交换性能的提升并没有那么明显,所以FPGA内部数据的交换越来越成为数据传输的瓶颈。为了解决这一问题,Achronix 在其最新基于台积电(TSMC)7nm FinFET工艺的Speedster7t FPGA器件中包

关键字:

NoC

1. 概述在摩尔定律的推动下,集成电路工艺取得了高速发展,单位面积上的晶体管数量不断增加。片上系统(System-on-Chip,SoC)具有集成度高、功耗低、成本低等优势,已经成为大规模集成电路系统设计的主流方向,解决了通信、图像、计算、消费电子等领域的众多挑战性的难题。 随着片上系统SoC的应用需求越来越丰富,SoC需要集成越来越多的不同应用的IP(Intellectual Property)。另外,片上多核系统MPSoC(MultiProcessor-System-on-Chip)也已经成

关键字:

NoC SoC

作为经过硅验证的创新型 片上网络 (NoC) 总线互连 IP 产品的领先供应商,Arteris IP 公司近日宣布 NETINT Technologies 公司再次获得 Arteris FlexNoC 总线互连 IP 技术的授权,此项技术将应用于其下一代带有片上视频编码处理器的企业级固态硬盘 (SSD) 存储系统控制器产品中。此前,NETINT 曾于 2019 年 1 月宣布首次购买 Arteris IP 总线互连许可授权(参见“ NETINT Techn

关键字:

NoC SSD

Arteris IP是一家经过硅验证的创新型 片上网络 (NoC) 互连 IP 产品的领先供应商,近日宣布芯擎科技获得 Arteris IP FlexNoC 总线互连和 FLexNoC Resilience 套件的IP授权,将其用作新一代汽车系统级芯片 (SoC) 总线连接的通信骨干网络。芯擎科技由中国汽车行业领导者吉利集团以及安谋科技(中国)有限公司共同出资成立。其产品将成为下一代汽车数字驾驶舱、导航和信息娱乐系统的芯片中枢。Arteris FlexNoC 不仅能够提升 SoC 性能

关键字:

NoC 安全

美国加利福尼亚州坎贝尔2019年4月18日消息—Arteris IP是经过实际验证的创新性片上网络(NoC)互连知识产权(IP)产品的全球领先供应商,今天宣布Baidu已购买Arteris IP FlexNoC互连,用于该公司的供数据中心使用的高性能昆仑人工智能云芯片。百度的昆仑人工智能云芯片是独一无二的产品,这是因为,无论它们是位于数据中心,还是位于车辆或消费电子等“周边”设备中,既能够进行人工智能训练,也能够进行推理,。百度首席架构设计师Jian Ouyang说:“Arteris的FlexNoc互连I

关键字:

云计算 百度 NoC

美国加利福尼亚州坎贝尔2019年04月11日消息—经过实际验证的创新性片上网络(NoC)互连知识产权(IP)产品的全球领先供应商Arteris IP,宣布推出新的Arteris IP FlexNoC版本4互连IP和配套的人工智能(AI)软件包。 FlexNoC 4和人工智能(“FlexNoC 4 AI”) 软件包实现了许多新技术,它们可以简化今天最复杂的人工智能(AI)、深度神经网络(DNN)和自主驾驶系统级芯片(SoC)的开发。 Arteris IP向一些世界领先的人工智能和深度学习(DN

关键字:

AI NoC IP

为了得到比传统片上网络的网络资源接口(NI)更高的数据传输效率和更加稳定的数据传输效果,提出了一种新的高效网络接口的设计方法,并采用Verilog HDL语言对相关模块进行编程,实现了高效传输功能,同时又满足核内路由的设计要求。最终通过仿真软件Xilinx ISE Design Suite 12.3和ModelSim SE 6.2b得到了满足设计要求的仿真结果。

关键字:

片上网络 网络资源接口 核内路由 Verilog HDL

这家在全世界领先的系统芯片(SoC)开发商使用FlexNoC互连结构IP作为其产品的片上通信骨干网络,用于连接现代系统芯片上的几十个或几百个IP块。按收入排名位居前三名的中国半导体企业,即深圳市海思半导体,展讯通信和锐迪科微电子,在他们最重要的系统芯片中使用Arteris公司的FlexNoC互连IP 。在大中华地区公开宣布采用Arteris公司的FlexNoC互连IP的其他客户包括全志科技,福州瑞芯微电子,珠海炬力和虹晶科技。据IHS iSuppli公司的数据,中国的大部分半导体公司得到授权使用Arter

关键字:

Ateris NoC 互联

IC制造技术的发展推动着芯片向更高集成度方向前进,从而能够将整个系统设计到单个芯片中构成片上系统SoC(System on Chip)。SoC采用全局同步型共享总线通信结构。这类系统由于挂在总线上的设备在通信时对总线的独占性

关键字:

FPGA ARM9 片上网络 系统

在FPGA 上设计一个高性能、灵活的、面积小的通信体系结构是一项巨大的挑战。大多数基于FPGA 的片上网络都是运行在一个单一时钟下。随着FPGA 技术的发展,Xilinx 公司推出了Virtex-4 平台。该平台支持同一时间内32 个

关键字:

FPGA 多时钟 片上网络

摘要 多核处理器已经成为处理器的主流,并发展成为各种通信与媒体应用的主流处理平台。通讯结构是多核系统中的核心技术之一,核间通信的效率是影响多核处理器性能的重要指标。目前有3种主要的通讯架构:总线系统结构

关键字:

关键 技术 架构 通讯 NoC 系统

本文介绍了一个基于FPGA 的高效率多时钟的虚拟直通路由器,通过优化中央仲裁器和交叉点矩阵,以争取较小面积和更高的性能。同时,扩展路由器运作在独立频率的多时钟NoC 架构中,并在一个3×3Mesh 的架构下实验,分析其性能特点,比较得出多时钟片上网络具有更高的性能。

关键字:

FPGA 多时钟 片上网络

片上网络(noc)介绍

您好,目前还没有人创建词条片上网络(noc)!

欢迎您创建该词条,阐述对片上网络(noc)的理解,并与今后在此搜索片上网络(noc)的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473