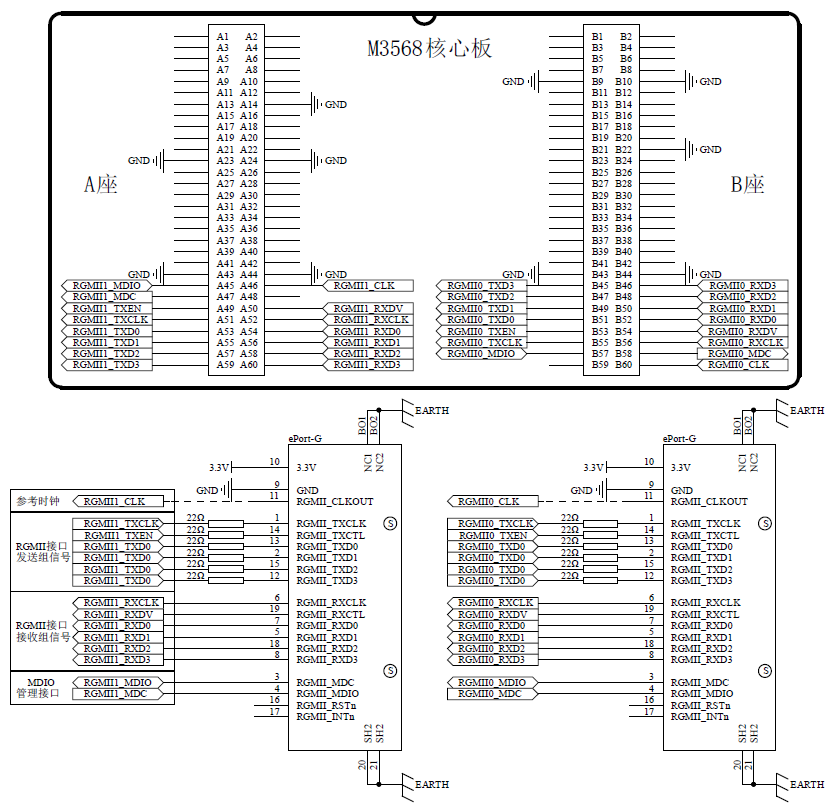

- 对同步通讯接口来说,时钟往往起着非常重要的作用。ePort-G模块的19个针脚上有四个是时钟信号,它们分别是:RGMII_MDC 、RGMII_TXCLK、RGMII_RXCLK以及RGMII_CLKOUT。这四个时钟信号分别代表什么?是输入还是输出?频率是多少?各自又起到什么作用?下面对这四个时钟信号进行简要介绍。ePort-G模块的19个针脚上有四个是时钟信号,它们分别有什么作用?本文为你解答。对同步通讯接口来说,时钟往往起着非常重要的作用。ePort-G模块的19个针脚上有四个是时钟信号,它们分别是

- 关键字:

ZLG 时钟信号

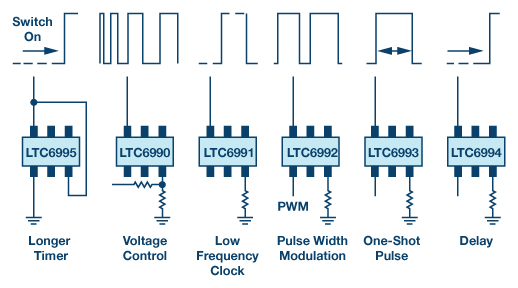

- 许多模拟电路需要一种时钟信号,或者要求能在一定时间后执行某项任务。对于这样的应用,有各种各样适用的解决方案。对于简单的时序任务,可以使用标准的555电路。使用555电路和适当的外部组件,可以执行许多不同的任务。然而,使用相当广泛的555定时器有一个缺点,就是设置不太精确。555定时器通过给外部电容充电和检测电压阈值来工作。这种电路很容易制作,但它的精度很大程度上取决于其电容的实际值。晶体振荡器适用于精度要求较高的应用。它们的精度可能很高,但它们有一个缺点:可靠性。参与电气设备维修的人都知道,故障通常是由大

- 关键字:

ADI 时钟信号

- 在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。在应用中,逻辑可能在上升沿、下降沿触发,或同时在上升沿和下降 沿触发。由于溢出给定时钟域的案例极多,故有必要插入缓冲器树来充足地驱动逻辑。时钟树通常带有布线工程师必须满足的延迟、歪曲率、最小功率及信号完整性 要求。 当电路从前工序设计人员转移到后工序布线工程师时,可以认为时钟概述与图表是必须沟通的最关键信息。多年以来,由于沟通失误,数以小时、天甚至是星期计的设计工作沦为白费,需要包括时钟树在内的全套重新

- 关键字:

布线工程师 时钟信号

- 这些时钟定义可能是也可能不是布线工程师需要定义时钟树根以在不同工作模式之间获得最优延迟 及平衡歪曲率的领域。前工序及布线工程师之间围绕这些信息的高级别信息沟通以及理解布线工程师怎样运用这些信息,将大幅优化物理设计流程的CTS过程。

- 关键字:

时钟信号 CTS 布线 数字电路

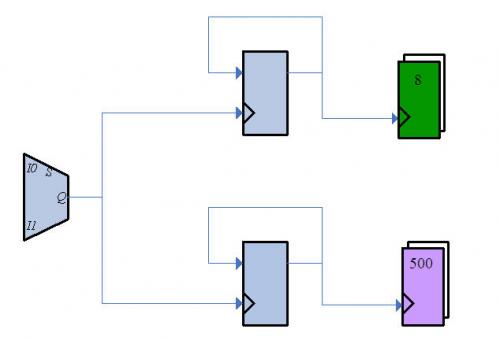

- 可以输1MHZ/2MHZ时钟信号的电路图如图所示可以输出1MHZ2MHZ两种信号供A/D转换器定时器/计数器串行接口使用。

- 关键字:

可以输 1MHZ 2MHZ 时钟信号

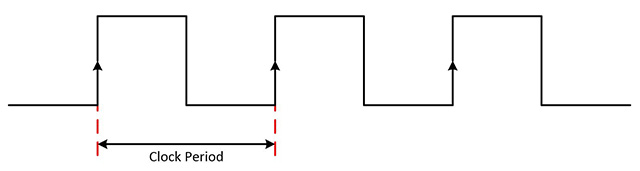

- 了解时钟信号的数字定时以及诸如抖动、漂移、上升时间、下降时间、稳定时间、迟滞和眼图等常用术语。 本教程是仪器基础教程系列的一部分。 1. 时钟信号 发送数字信号其实发送的就是一串由0或1组成的数字序列。 然而,与不同设备进行通信时,定时信息要与发送的位相关联。 数字波形作为时钟信号的参考。 您可以将时钟信号看成是一个指挥者,它为数字电路系统的各个部分提供定时信号,使每个过程都可在精确的时间点触发。 时钟信号是具有固定周期的方波。 周期是

- 关键字:

数字定时 时钟信号

- 在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。

- 关键字:

Xilinx FPGA RAM DCM 时钟信号

- 在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。在应用中,逻辑可能在上升沿、...

- 关键字:

布线工程师 时钟信号

- 带宽是大多数工程师在选择一款示波器时首先考虑的参数。本文将为您提供一些有用的窍门,教您如何为您的数字和模拟应用选择合适的示波器带宽。

- 关键字:

示波器 带宽 时钟信号

- 您在使用一个高速模数转换器(ADC)时,总是期望性能能够达到产品说明书载明的信噪比(SNR)值,这是很正常的事情。...

- 关键字:

高速 ADC 时钟信号

- 在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。在应用中,逻辑可能在上升沿、下降沿触发,或同时在上升沿和下降沿触发。由于溢出给定时钟域的案例极多,故有必要插入缓冲器树来充

- 关键字:

布线 工程师 时钟信号

- (1)MCLK 系统主时钟。除了CPU 运算使用此时钟信号外,外围模块也可以使用。MCLK 可以选择任何一个振荡器产生 ...

- 关键字:

MSP430 时钟信号 振荡器

- 一、I2C总线介绍: 由于大规模集成电路技术的发展,在单个芯片集成CPU以及组成一个单独工作系统所必须的ROM ...

- 关键字:

I2C 总线协议 时钟信号

时钟信号介绍

您好,目前还没有人创建词条时钟信号!

欢迎您创建该词条,阐述对时钟信号的理解,并与今后在此搜索时钟信号的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473