- 时钟分频在之前的实验中我们已经熟悉了小脚丫的各种外设,掌握了verilog的组合逻辑设计,接下来我们将学习时序逻辑的设计。====硬件说明====时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频率非常高的基本设计之一。一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。在本实验中我们将实现任意整数的分频器,分频的时钟保持50%占空比。1,偶数分频:偶数倍分频相对简单,比较容易理解。通

- 关键字:

时序逻辑 时钟分频 FPGA Lattice Diamond 小脚丫

- 时钟分频在之前的实验中我们已经熟悉了小脚丫的各种外设,掌握了verilog的组合逻辑设计,接下来我们将学习时序逻辑的设计。硬件说明时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频率非常高的基本设计之一。一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。在本实验中我们将实现任意整数的分频器,分频的时钟保持50%占空比。1,偶数分频:偶数倍分频相对简单,比较容易理解。通过计数器计数是完

- 关键字:

时序逻辑 时钟分频 FPGA Lattice Diamond 小脚丫

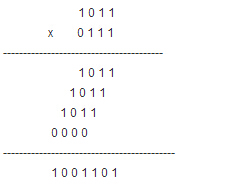

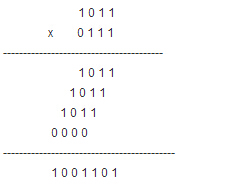

- 上次看了一下关于乘法器的Verilog代码,有几个地方一直很迷惑,相信很多初学者看这段代码一定跟我当初一样,看得一头雾水,在网上也有一些网友提问,说这段代码不好理解,今天小墨同学就和大家一起来看一下这段代码,我会亲自在草稿纸上演算,尽量把过程写的详细些,让更多的人了解乘法器的设计思路。

下面是一段16位乘法器的代码,大家可以先浏览一下,之后我再做详细解释

module mux16(

clk,rst_n,

start,ain,bin,yout,done

);

inpu

- 关键字:

FPGA Verilog 时序逻辑

- 寄存器传输级(RTL)验证在数字硬件设计中仍是瓶颈。行业调研显示,功能验证占整个设计工作的70%。但即使把重点放在验证上面,仍有超过60%的设计出带需要返工。其主要原因是在功能验证过程中暴露出来的逻辑或功能瑕疵和

- 关键字:

RTL 时序逻辑 等效 检查方法

- 寄存器传输级(RTL)验证在数字硬件设计中仍是瓶颈。行业调研显示,功能验证占整个设计工作的70%。但即使把重点放在验证上面,仍有超过60%的设计出带需要返工。其主要原因是在功能验证过程中暴露出来的逻辑或功能瑕疵和

- 关键字:

时序逻辑 等效 检查方法 风险

时序逻辑介绍

时序逻辑 由多个触发器和多个组合逻辑块组成的网络。常用的有:计数器、复杂的数据流动控制逻辑、运算控制逻辑、指令分析和操作控制逻辑。同步时序逻辑是设计复杂的数字逻辑系统的核心。时序逻辑借助于状态寄存器记住它目前所处的状态。在不同的状态下,即使所有的输入都相同,其输出也不一定相同。 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473