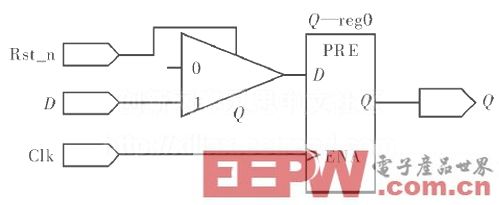

- 异步复位,同步释放的方式,而且复位信号低电平有效-顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。

- 关键字:

异步复位 低电平

- FPGA开发技巧之同步复位与异步复位的理解-前两天和师兄讨论了一下design rule其中提到了同步异步复位的比较这个常见问题,据说也是IC公司经常问到的一面试题。

- 关键字:

FPGA 同步复位 异步复位

- 异步复位同步释放 首先要说一下同步复位与异步复位的区别。 同步复位是指复位信号在时钟的上升沿或者下降沿才能起作用,而异步复位则是即时生效,与时钟无关。异步复位的好处是速度快。 再来谈一下为什么FPGA设计中要用异步复位同步释放。 复位信号的释放是有讲究的: 我们知道,DFF的D端和clk端之间时序关系是有约束的,这种约束我们通过setup time和hold time来 check。即D端的data跳变的时刻要与clk端的时钟上升沿(或者下降沿)跳变要错开,如果

- 关键字:

FPGA 异步复位

- 对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局异步复位/置位

- 关键字:

FPGA 复位可靠性 同步复位 异步复位

- 对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局异步复位/置位资源和采用内部复位。上述方法可有效提高FPGA复位的可靠性。

对FPGA芯片而言,在给芯片加电工作前,芯片内部各个节点电位的变化情况均不确定、不可控,而这种不确定且不可控的情况会使芯片在上电后的工作状态出现错误。因此,在FPGA的设计中,为保证系统能可靠进进入工作状态,以及避免对FPGA输

- 关键字:

FPGA 异步复位 异步复位

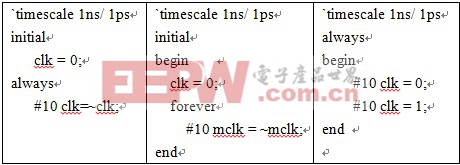

- Testbench,就是测试平台的意思,具体概念就多不介绍了,相信略懂FPGA的人都知道,编写Testbench的主要目的是为了对使用硬件描述语言(HDL)设计的电路进行仿真验证,测试设计电路的功能、部分性能是否与预期的目标相符。

- 关键字:

FPGA Quartus Testbench 开发板 异步复位

异步复位介绍

您好,目前还没有人创建词条异步复位!

欢迎您创建该词条,阐述对异步复位的理解,并与今后在此搜索异步复位的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473