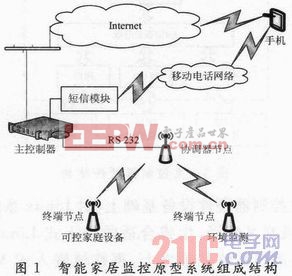

- 摘要:为了实现用户随时随地对家庭的监测和控制,在此以智能家居监控系统为研究对象,设计了一种智能家居监控原型系统。设计的基于Android的手机客户端,使用户可以在任何能够连接Internet的地方轻松方便地实现对家庭

- 关键字:

设计 系统 原型 监控 智能家居

- 标签:高清视频 编解码日前,北京亚科鸿禹电子有限公司发布一套基于其最新研发的原型验证系统“VeriTiger-DH2000T” 的应用设计。将高清视频采集,H.264数据压缩,H.264数据解压缩,1080P/60Hz视频显示等

- 关键字:

视频 解码 设计 高清 系统 原型 验证 基于

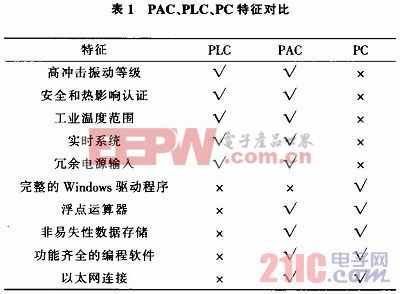

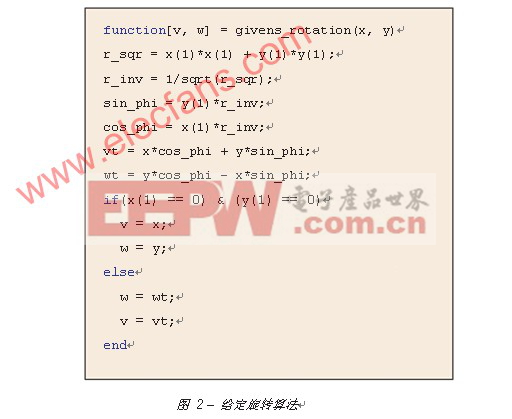

- 摘要:电机控制器的开发是电动汽车开发中的重要环节。文中提出了一种基于NI Compact RIO可编程自动化控制器(PAC)的电机控制器快速控制原型(RCP)的方法。通过对PAC的主要架构、功能、实现形式进行阐述,结合永磁同步电

- 关键字:

控制 原型 研究 快速 控制器 PAC 电机 基于

- 1 背景介绍在日益信息化的社会中,各种各样的嵌入式系统已经全面渗透到日常生活的每一个角落。嵌入式系统的功能越来越复杂,这就使得一个嵌入式系统产品从市场需求立项到方案选择、样机研制、定型量产所需要的开发费

- 关键字:

平台 方案 原型 快速 ARM 基于

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

EMC 仿真 原型 耦合

- 空间复用式多输入多输出 (MIMO) 发射器与接收器据称可比其现有的单输入单输出 (SISO) 对应器件提升更大的无线通信系统性能。下一代无线标准,如 802.11n,将支持高达 600 Mbps 数据传输速率和超过 1 GHz 的无线局域网

- 关键字:

验证 方法 介绍 设计 原型 系统 快速 MIMO

- 内嵌ARM9E内核系统级芯片的原型验证方法,【摘要】随着大容量高速度的FPGA的出现,在流片前建立一个高性价比的原型验证系统已经成为缩短系统级芯片(SoC)验证时间,提高首次流片成功率的重要方法。本文着重讨论了用FPGA建立原型进行验证的流程、优缺点以及常

- 关键字:

原型 验证 方法 芯片 系统 ARM9E 内核 内嵌

- SoC原型验证技术的研究 北京清华大学微电子所(100084) 马凤翔 孙义和 摘 要:快速系统原型技术已成为SoC(片上系统)验证的主要手段之一,但大多数的原型描述仍使用Verilog/VHDL语言,描述效率低。以软件编译式系统设计(SCSD)为基础,提出了SoC的原型验证流程,用Handel-C语言描述SoC原型,并直接实现在原型验证硬件上;用SCSD的软件工具、RC1000和RC200硬件平台搭建了一个SoC原型验证系统的样机,并在样机上完成了Lena图像处理SoC的原型验证;在反复

- 关键字:

Handel-C SoC 软件编译式系统设计 验证 原型 SoC ASIC

- 该芯片能够有选择性地收集和移动生物制剂的大分子, 预示低成本和自动化的医学诊断生物样本制备时代即将来临 世界微流控芯片的主要供应商意法半导体 (纽约证券交易所代码:STM)公布了一个完整的能够收集处理特定的生物大分子的芯片原型。配合ST的经过市场验证的片上实验室技术,ST的研发计划正在为让医学和法医生物样品快速制备、分析和评估过程实现自动化的低成本一次性芯片铺平道路。 市场上现有的技术先进的生物技术平台如ST的 In-CheckTM “片上

- 关键字:

处理芯片 单片机 嵌入式系统 生物样品制备 意法半导体(ST) 原型

- 随着数字集成电路(IC)的设计变得更加复杂,验证其功能的工作也越来越复杂了。在能被设计的门电路数量和能在合理时间内被验证的门电路数量之间一直存在差距,而这些年来,EDA 厂商们在缩小这种差距方面几乎无所作为。 要 点 ●加快的速度是RTL仿真的10至 50倍。 ●新仿真方法的速度是RTL仿真的1000至5000倍。 ●FPGA原型的速度可以达到 RTL仿真的10,000倍。 ●EDA厂商目前提供可简化构建原型的分

- 关键字:

ASIC 构建 原型

原型介绍

您好,目前还没有人创建词条原型!

欢迎您创建该词条,阐述对原型的理解,并与今后在此搜索原型的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473