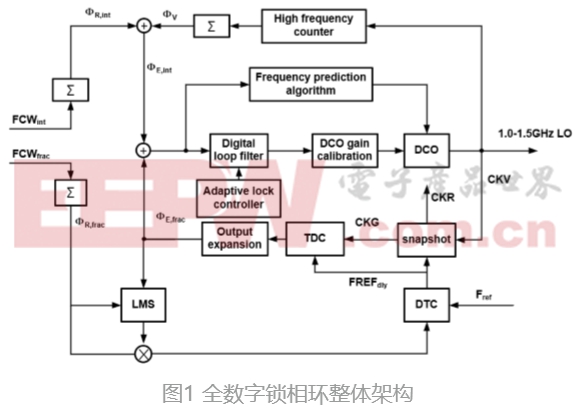

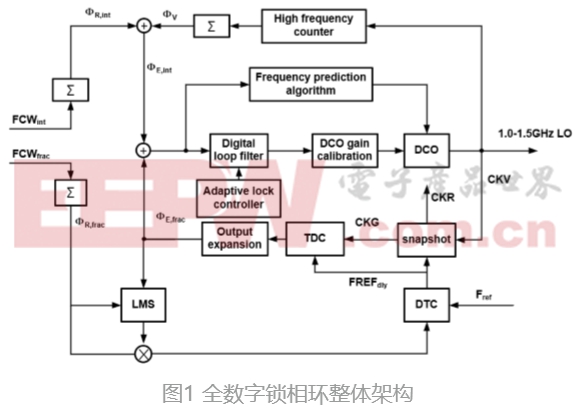

- 谭宁禹 (大连理工大学 微电子学院,辽宁 大连 116024)摘 要:近年来,5G和物联网应用对片上系统时钟提出了新的需求。锁相环在片内发挥着重要的作用,以产 生不同的时钟源。这些新需求的主要关注点快速锁定、低功耗、低噪声和小面积。随着CMOS工艺的发展,模 拟锁相环的工作电压逐渐降低,其设计面临着巨大的挑战。根据市场需求,采用全数字锁相环(ADPLL)进行数 字设计,以减少设计时间和设计工作量。此外,使用标准单元实现的ADPLL不仅可以加快设计时间,而且可以 提高可移植性。当系统处于休眠状态时,锁相环

- 关键字:

202003 全数字锁相环 快速锁定 频率预测算法

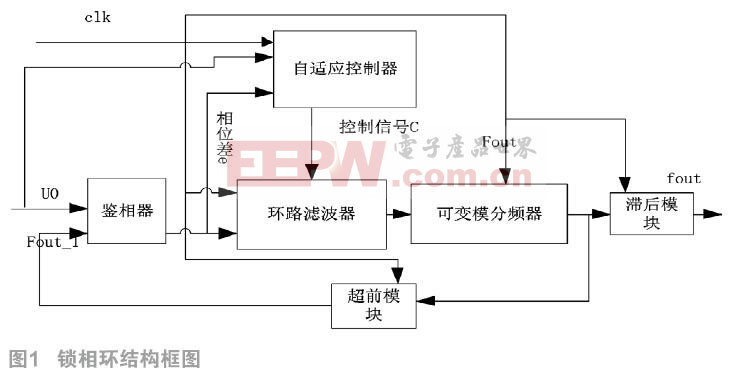

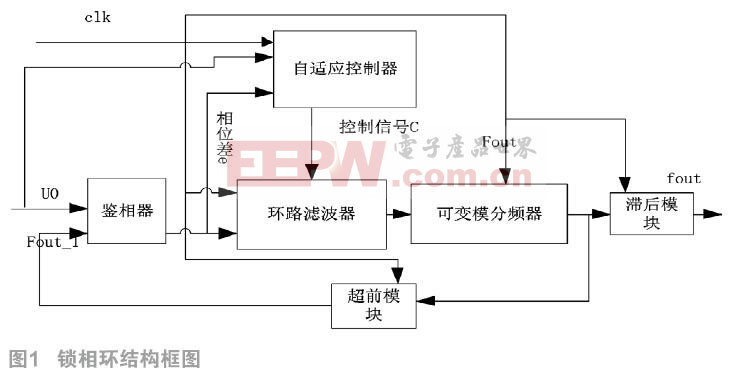

- 针对无线电能传输频率跟踪设计中传统锁相环电路设计复杂、跟踪速度慢、锁相频带窄和无超前滞后环节,单独模块设计修改繁琐等问题,对自变模全数字锁相环进行改进, 与传统的全数字锁相环相比,该锁相环采用可变模分频器,使得中心频率可变,锁相范围增大;通过前馈回路进行鉴频调频,提高了锁相速度;同时,其环路滤波器采用比例积分结构,使得锁相输出无静差且比例积分参数依据相位差自动进行调节;通过参数设置可调节输出信号的相位。应用modelsim进行仿真,并进行实物验证证实了该设计具有宽范围的锁相能力及快速精确的频率跟踪性能。

- 关键字:

全数字锁相环 比例积分控制 FPGA 无线电能传输 201706

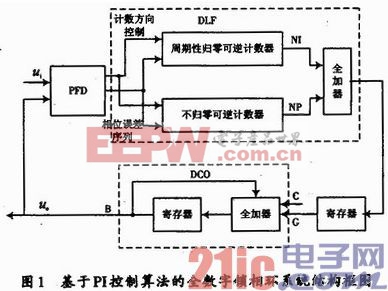

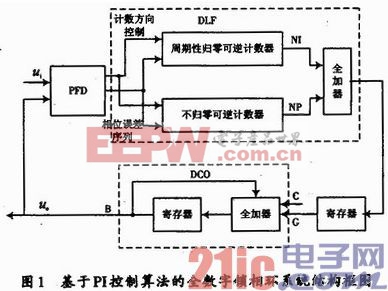

- 针对以往全数字锁相环研究中所存在电路结构复杂、设计难度较大和系统性能欠佳等问题,提出了一种实现全数字锁相环的新方法。该锁相环以数字比例积分控制的设计结构取代了传统的一些数字环路滤波控制方法。应用EDA技术完成系统设计,并进行计算机仿真。仿真结果表明:在一定的频率范围内,该锁相环锁定时间最长小于15个输入信号周期,相位抖动小于输出信号周期的5%,且具有电路结构简单、环路性能好和易于集成的特点。

- 关键字:

比列积分控制 全数字锁相环 超高速集成电路硬件描述语言 现场可编程门阵列

- 摘要:本文在说明全数字锁相环的基础上,提出了一种利用FPGA设计一阶全数字锁相环的方法,并给出了关键部件的RTL可综合代码,并结合本设计的一些仿真波形详细描述了数字锁相环的工作过程,最后对一些有关的问题进行了讨论。关键词:全数字锁相环;DPLL;FSK;FPGA 引言锁相环(PLL)技术在众多领域得到了广泛的应用。如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的PLL相比,具有精度高且不受温度和电压影响,环路

- 关键字:

DPLL FPGA FSK 全数字锁相环

全数字锁相环介绍

您好,目前还没有人创建词条全数字锁相环!

欢迎您创建该词条,阐述对全数字锁相环的理解,并与今后在此搜索全数字锁相环的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473