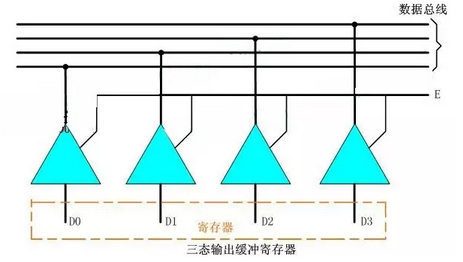

- 为减少信息传输线的数目,大多数计算机中的信息传输线均采用总线形式,即凡要传输的同类信息都走同一组传输线,且信息是分时传送的。在计算机中一般有三组总线,即数据总线、地址总线和控制总线。为防止信息相互干扰,要求凡挂在总线上的寄存器或存储器等,它的传输端不仅能呈现0、1两个信息状态,而且还应能呈现第三种状态——高阻抗状态(又称高阻状态),即此时好像它们的输出被断开,对总线状态不起作用,此时总线可由其它器件占用。三态门即可实现上述的功能,它除具有输入输出端之外,还有一控制端,请看下图。

- 关键字:

三态门 三态缓冲器

三态缓冲器介绍

三态缓冲器(Three -state Buffer)又称为三态门、三态驱动器,其三态输出受使能输入端的控制,当使能输入有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1);当使能输入无效时,输出处于高阻状态,即等效于与所连接的电路断开。 三态缓冲器不仅有输入输出端口,还有一个控制端。 当控制端EA = 1时,输出=输入,总线由该器件驱动,总线上的数据即为输入端的数据; 当控制端EA = 0 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473