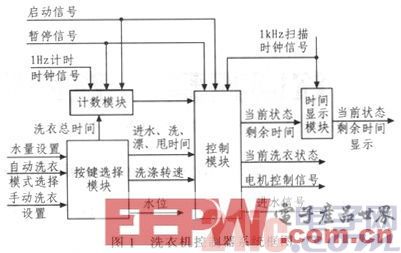

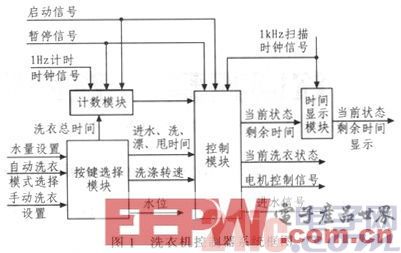

- 摘要:为降低设计成本,缩短设计周期,提出一种基于VHDL的洗衣机控制器的设计方案。该方案采用模块化的设计思想,并使用状态机完成控制模块的设计。整个系统在QuartusⅡ开发平台上完成设计、编译和仿真,并在FPGA硬件实验箱上进行测试。仿真波形和测试结果均表明该设计方案切实可行。

为提高洗衣机控制系统的智能性,以及定时和转速的精确度,目前洗衣机控制系统通常采用数字电路而不是传统的机械式控制。随着EDA(Electronic Design Automation,电子设计自动化)技术的发展,采用硬件描述语言在

- 关键字:

FPGA VHDL

- 作为一个负责FPGA 企业市场营销团队工作的人,我不得不说,由于在工艺技术方面的显著成就以及硅芯片设计领域的独创性,FPGA 正不断实现其支持片上系统设计的承诺。随着每一代新产品的推出,FPGA 在系统中具有越来来越多的功能,可作为协处理器、DSP 引擎以及通信平台等,在某些应用领域甚至还可用作完整的片上系统。 因此,在摩尔定律的作用下,FPGA 产业的门数量不断增加,性能与专门功能逐渐加强,使得 FPGA 在电子系统

- 关键字:

xilinx FPGA VHDL Verilog

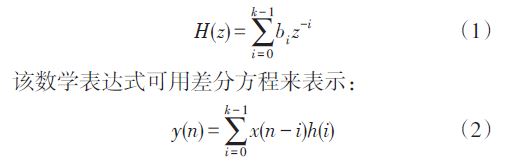

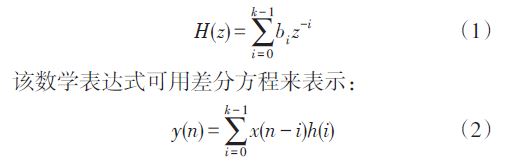

- 利用VHDL语言设计数字滤波器,主要在于如何实现乘法。乘法常用的实现方法有位串行乘法、分布式算法和并行乘法等。位串行乘法能节省大量硬件资源,但运算周期过长,对于数字滤波器这种高速率要求不宜采取。分布式算法是现在比较流行的一种乘法实现方式,所用硬件资源较少,运算速率也较快,但这只是针对小位宽乘法来说。对于数字滤波器的较大位宽的乘法,不宜采取。并行乘法,算法实现简单直观,对于现在资源丰富的FPGA,很好实现

- 关键字:

滤波器 数字 FPGA VHDL

- 0 引言

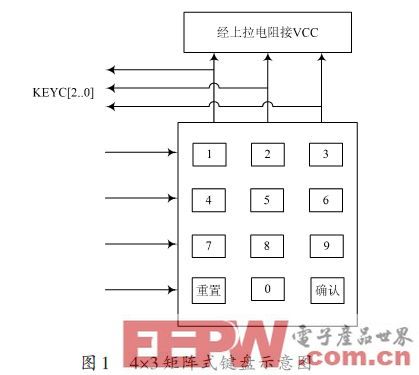

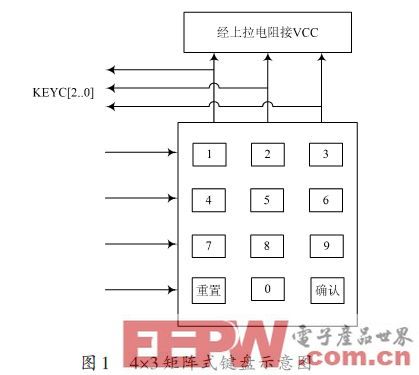

传统机械锁的防盗功能差,在现代高科技安防系统中无法起到作用,已逐步被更可靠、更智能的电子数字密码锁代替。目前市场上的大部分密码锁产品是以单片机为核心的,利用软件进行控制,实际应用中系统稳定性较差且成本高。本文研究的是电子密码锁的一种纯硬件实现方案,为弥补传统技术的不足,采用EDA技术在可编程芯片上实现密码的存储、运算等操作,使产品既具有硬件的安全性和高速性,又具有软件开发的灵活性和易维护性。

1 主要技术与开发环境

1.1 EDA技术及特点

EDA(Electronic Design A

- 关键字:

FPGA VHDL

- 在数字系统的设计中,FPGA+ARM的系统架构得到了越来越广泛的应用,FPGA主要实现高速数据的处理;ARM主要实现系统的流程控制。人机交互。外部通信以及FPGA控制等功能。I2C、SPI等串行总线接口只能实现FPGA和ARM之间的低速通信; 当传输的数据量较大。要求高速传输时,就需要用并行总线来进行两者之间的高速数据传输。

- 关键字:

FPGA ARM DATA VHDL 数据总线

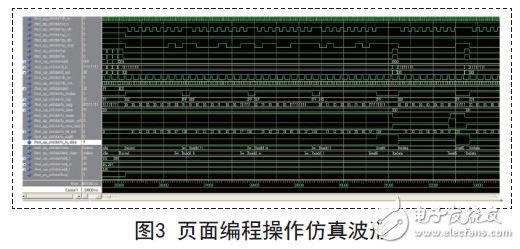

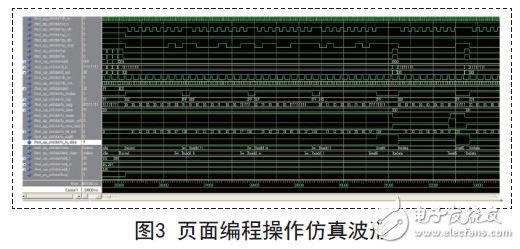

- 本文提出一个基于FPGA的SPI Flash读写硬件实现方案,该方案利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新及预充电等操作,同时编写的SPI Flash控制器IP核能够进行移植和复用,作为SOC芯片的功能模块。

- 关键字:

FPGA Flash SOC CPU VHDL

- 在Matlab/Simulink环境下,采用DSP Builder模块搭建FIR模型,根据FDATool工具对FIR滤波器进行了设计,然后进行系统级仿真和ModelSim功能仿真,其仿真结果表明其数字滤波器的滤波效果良好。

- 关键字:

DSP FPGA VHDL 滤波器 FIR

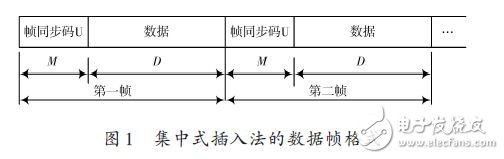

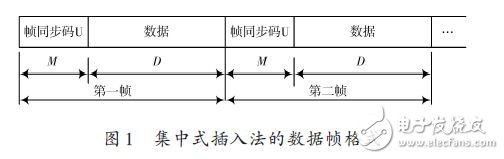

- 在Xilinx的FPGA器件XC3S200-4FT200上对方案中设计的帧同步系统进行了实现,利用Modelsim 6.0软件进行了仿真测试。仿真结果表明,本方案设计的同步系统工作稳定,满足性能要求。

- 关键字:

Xilinx FPGA 帧同步 VHDL 寄存器

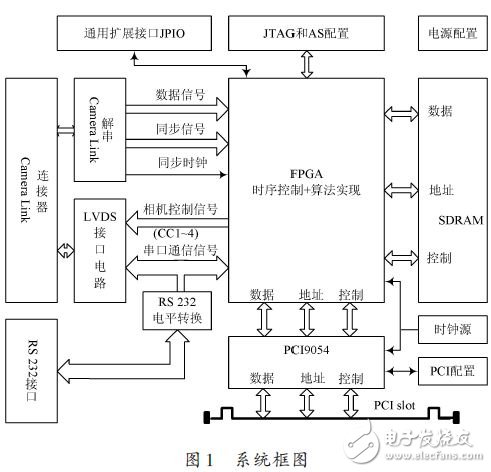

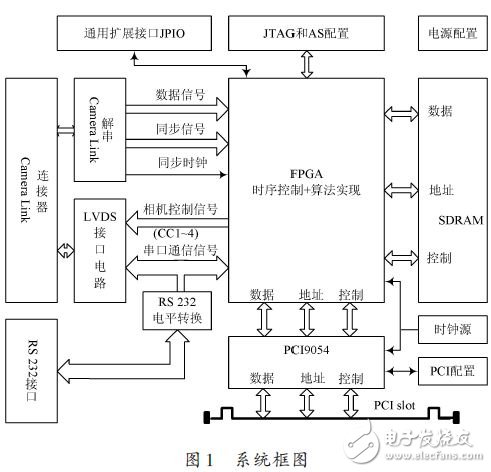

- 图像在采集过程中不可避免地会受到传感器灵敏度、噪声干扰以及模数转化时量化问题等因素影响而导致图像无法达到人眼的视觉效果,为了实现人眼观察或者机器自动分析的目的,对原始图像所做的改善行为,就被称作图像增强技术。

- 关键字:

传感器 图像增强 FPGA PCI VHDL

- 文中详细介绍了QPSK技术的工作原理和QPSK调制、解调的系统设计方案,并通过VHDL语言编写调制解调程序和QuaitusII软件建模对程序进行仿真,通过引脚锁定,下载程序到FPGA芯片EP1K30TC144-3中验证。软件仿真和硬件验证结果表明了该设计的正确性和可行性,由于采用FPGA芯片,减小了硬件设计的复杂性,该设计具有便于移植维护和升级的特点。

- 关键字:

VHDL QPSK 调制解调系统 设计与仿真

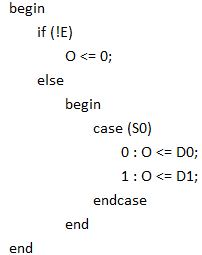

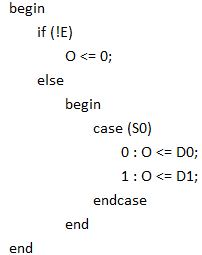

- 4.5.1 always块语言指导原则使用always块进行可综合的代码设计时需要注意以下几个问题。(1)每个always块只能有一个事件控制“@(event-expression)”,而且要紧跟在always关键字后面。(2)always块可以表示

- 关键字:

VHDL 进阶 代码设计 逻辑

- 从大学时代第一次接触FPGA至今已有10多年的时间。至今记得当初第一次在EDA实验平台上完成数字秒表,抢答器,密码锁等实验时,那个兴奋劲。当时由于没有接触到HDL硬件描述语言,设计都是在MAX+plus II原理图环境下用74系列逻辑器件搭建起来的。

- 关键字:

FPGA EDA VHDL Verilog 时钟 IP核

- 为了实现靶场时统终端输出IRIG-B标准DC code信号,采用VHDL语言在FPGA逻辑电路中设计了DC code编码器硬件电路,通过QuartusⅡ软件建立工程文件对VHDL语言DC code编码器电路进行编译和仿真,获得了符合IRIG-B标准的DC code信号。经过实践验证,该电路具有实现方法简单、电路稳定性好、精度高的特点,实测同步精度小于1μs。

- 关键字:

IRIG-B FPGA code VHDL

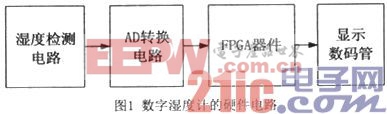

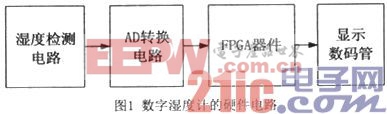

- 湿度计是一种常用的检测仪器,文中利用FPGA器件与HS1101湿度传感器设计实现了一种简易的数字湿度计,用于检测室内湿度。该湿度计具有结构简单、测量准确性高、稳定性好等优点。

- 关键字:

湿度 湿度传感器 VHDL FPGA

- 概述随着电子设计自动化(EDA)技术的发展,可编程逻辑器件FPGA/CPLD已经在许多方面得到了广泛应用,而UART(通用异步收发器) 是在数字通信和控制系统中广泛使用的串行数据传输协议。因此越来越多用户根据自己的需要,以

- 关键字:

FPGA UART VHDL 倍频

vhdl.programming介绍

您好,目前还没有人创建词条vhdl.programming!

欢迎您创建该词条,阐述对vhdl.programming的理解,并与今后在此搜索vhdl.programming的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473