上周我跟我同事说,“ 两种语言阻碍了嵌入式系统开发人员和软件工程师借助Zynq SOCs来提升系统性能。”那就是“Verilog” 和 “VHDL”正如期待那样,这已经得到了解决—因为SD

关键字:

Verilog VHDL SDSoC

某定向设备采用多普勒效应测向原理,即当天线振子做圆周运动时,天线振子本身与目标信号源就会产生相对速度,使振子感应到的信号产生了多普勒频移,通过对振子感应信号相位的处理,从而达到测向的目的。而为了提高天

关键字:

FPGA VHDL 选通电路 分频

随着科学研究与技术开发市场化,采用传统电子设计手段在较短时间内完成复杂电子系统设计,已经越来越难完成了。EDA(EleCTRonICs Design Automation)技术是随着集成电路和计算机技术飞速发展应运而生一种高级、快速、有效电子设计自动化工具。 1、EDA技术 EDA(电子线路设计座自动化)是以计算机为工作平台、以硬件描述语言(VHDL)为设计语言、以可编程器件(CPLD/FPGA)为实验载体、以ASIC/SOC芯片为目标器件、进行必要元件建模和系统仿真电子产品自

关键字:

EDA VHDL

这次我们讲一讲如何入门学习硬件描述语言和数字逻辑电路;学习数字逻辑电路,我推荐的一本书就是--《数字设计-原理与实践》,其他的深入点可以看看《完整数字设计》;而对于硬件描述语言呢?有两个原则,一个是买书的原则,一个是看书的原则。首先,你必须买两类书,一类是语法书,平常使用的时候可以查一查某些语法;一类是,对语言的使用的讲解和使用的方法(如何书写RTL,如何设计电路,如何调试代码,使用仿真器等);我用过一年的VHDL和两年的Verilog;作为过来人,我想介绍一些比较好的书给入门者,避免大家走弯路。

关键字:

VHDL Verilog

引 言

电动机是各类数控机床的重要执行部件。要实现对电动机的精确位置控制,转子的位置必须能够被精确的检测出来。光电编码器是目前最常用的检测器件。光电编码器分为增量式、绝对式和混合式。其中,增量式以其构造简单,机械寿命长,易实现高分辨率等优点,已被广泛采用。增量式光电编码器输出有A,B,Z三相信号,其中A相和B相相位相差90°,Z相是编码器的“零位”,每转只输出一个脉冲。在应用中,经常需要对A相、B相正交脉冲按照一定的比例,即分周比进行分频。分频的难点是,无论设定分

关键字:

FPGA VHDL

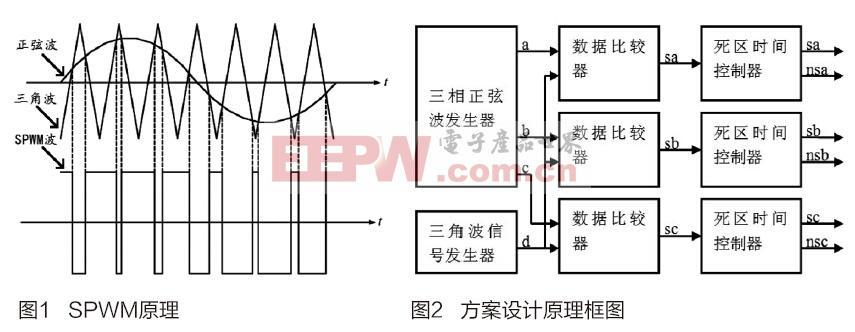

本文提出了一种采用VHDL硬件描述语言设计新型三相正弦脉宽调制(SPWM)波形发生器的方法。该方法以直接数字频率合成技术(DDS)为核心产生三相SPWM信号。并且利用VHDL设计了死区时间可调的死区时间控制器,解决了传统的模块电路等待方法很难产生带精确死区时间控制的SPWM信号的问题。该方法在Quartus II 9.1环境平台下进行了仿真验证,并将设计程序下载到DE2-70实验板进行实验测试,用示波器测试得到了死区时间可控制的SPWM波形。

关键字:

VHDL SPWM DDS 死区时间 FPGA 201505

引 言

FPGA 即现场可编程逻辑阵列。是在CPLD 的基础上发展起来的新型高性能可编程逻辑器件。FPGA的集成度很高,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与组合逻辑电路功能,适用于高速、高密度的高端数字逻辑电路设计领域。新一代的FPGA 甚至集成了中央处理器( CPU ) 或数字处理器( DSP) 内核,在一片FPGA 上进行软硬件协同设计,为实现片上可编程系统( SOPC) 提供了强大的硬件支持。对微型打印机的驱动,传统方法是使用单片机是实现对其的时序控制。随着FPGA

关键字:

FPGA VHDL

VHDL是随着可编辑逻辑器件(PLD)的发展而发展起来的一种硬件描述语言。它是1980年美国国防部VHSIC(超高速集成电路)计划的一部分,并于1986年和1987年分别成为美国国防部和IEEE的工业标准。作为一种硬件设计时采用的标准语言,VHDL具有极强的描述能力,能支持系统行为级、寄存器传输级和门级三个不同层次的设计,这样设计师将在TOP-DOWN设计的全过程中均可方便地使用同一种语言。而且,VHDL设计是一种“概念驱动式”的高层设计技术,设计人员毋需通过门级原理图描述电路

关键字:

VHDL

心率监控器是一款用于监测人体心跳速率的器件。心率的单位是bpm(每分钟心跳数)。人体的心跳速率根据其日常身体活动、睡眠和基本健康状况的不同而有所差别。本文为大家介绍几种心率计及心率监测系统的设计,供大家使用参考。

基于EFM32TG840的便携式心率计的设计方案

在消费电子领域,便携式电子产品由于体积小、质量轻的特点越来越受到消费者的喜爱,已成为人们生活中不可缺少的部分。基于这个思路,我们设计了一款便携式心率计,它可以替代用脉搏听诊器等进行测量的传统方法,使用非常方便。

一种便携式单

关键字:

FPGA VHDL

图像传感器,或称感光元件,是一种将光学图像转换成电子信号的设备,它被广泛地应用在数码相机和其他电子光学设备中。早期的图像传感器采用模拟信号,如摄像管(video camera tube)。如今,图像传感器主要分为感光耦合元件(charge-coupled device, CCD)和互补式金属氧化物半导体有源像素传感器(CMOS Active pixel sensor)两种。本文介绍基于CMOS或CCD两种图像传感器的应用及技术文献,供大家参考。

基于USB传输及CMOS图像传感器的指纹识别仪的实

关键字:

Verilog HDL QuartusⅡ VHDL

FIR滤波器,有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。本文着重介绍基于不同结构的FIR滤波器的设计方案,供大家参考。

基于FPGA 的FIR 数字滤波器设计方案

基于FPGA分布式算法的低通FIR滤波器的设计与实现

二维FIR滤波器的FPGA实现

基于XC2V10

关键字:

Simulink VHDL EDA技

用CPLD设计所构成的CPI接口系统具有简洁、可靠等优点,是一种行之有效的设计途径。很多技术杂志和网站上,都有不少用CPLD设计PCI 常规传输系统的文章。但用这些方法在MzxPlusII、Fundition等环境下进行模拟仿真时,其产生的时序往往与PCI规范有很大出入。虽然 Altera 等公司推出PCI核可以直接使用,但这样的内核占用CPLD资源较多,且能适配的器件种类少,同时价格也高,在实际设计应用中有很大的局限性。因此,使用通用型CPLD器件设计简易型PCI接口有很大的现实意义。在Compac

关键字:

PCI VHDL-CPLD Compact接口

1引言

随着社会的发展。使用电梯越来越普遍,已从原来只在商业大厦、宾馆过渡到在办公室、居民楼等多种建筑中,并且对电梯功能的要求也不断提高,其相应控制方式也在不断发生变化。电梯的微机化控制主要有:PLC控制、单板机控制、单片机控制、单微机控制、多微机控制和人工智能控制等。随着EDA技术的快速发展,PLD器件已广泛应用于电子设计与控制的各个方面。这里使用CPLD器件,采用VHDL语言设计一个16楼层单个载客箱的电梯控制系统,此控制系统具有使用安全可靠,功能全面的特点,方便人们生活。

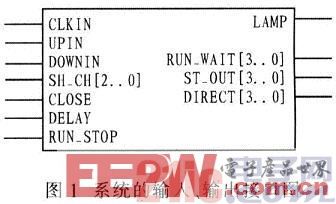

2系统总体

关键字:

CPLD VHDL 电梯

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起来的。它是一种面向设计、多层次的硬件描述语言,是集行为描述、RTL描述、门级描述功能为一体的语言,并已成为描述、验证和设计数字系统中最重要的标准语言之一。由于VHDL在语法和风格上类似于高级编程语言,可读性好,描述能力强,设计方法灵活,可移植性强,因此它已成为广大EDA工程师的首选。目前,

关键字:

FPGA CPLD VHDL

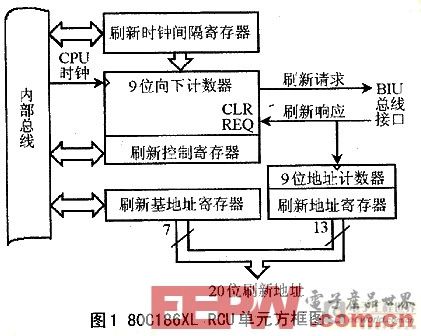

80C186XL16位嵌入式微处理器是Intel公司在嵌入式微处理器市场的上导产品之一,已广泛应用于电脑终端、程控交换和工控等领域。在该嵌入式微处理器片内,集成有DRAM RCU单元,即DRAM刷新控制单元。RCU单元可以自动产生DRAM刷新总线周期,它工作于微处理器的增益模式下。经适当编程后,RCU将向将处理器的 BIU(总线接口)单元产生存储器读请求。对微处理器的存储器范围编程后,BIU单元执行刷新周期时,被编程的存储器范围片选有效。

存储器是嵌入式计算机系统的重要组成部分之一。通常采用静态

关键字:

CPLD DRAM VHDL

vhdl.programming介绍

您好,目前还没有人创建词条vhdl.programming!

欢迎您创建该词条,阐述对vhdl.programming的理解,并与今后在此搜索vhdl.programming的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473