sdram-based 文章 进入sdram-based技术社区

MIPS授权中科院计算技术研究所使用MIPS架构

- MIPS 科技公司宣布,中国科学院计算技术研究所已获得 MIPS32 和 MIPS64 架构授权,以进一步推动龙芯系列处理器的开发与商业化工作。在 2007 年,MIPS 科技的授权客户意法半导体(STMicroelectronics)选用 MIPS64 架构来支持 ICT 的龙芯处理器研发。本次则是该机构首度直接取得 MIPS 架构授权。 中国科学院计算技术研究所(ICT)所长李国杰先生表示:“我们非常高兴能与 MIPS 强化合作关系,以持续推动新技术在中国的创新与采用。业界标准

- 关键字: MIPS 龙芯 MIPS32 MIPS64 MIPS-based

MIPS科技宣布推出在MIPS架构上的Android平台

- 为家庭娱乐、通信、网络和便携多媒体市场提供业界标准处理器架构和内核的领导厂商 MIPS 科技公司(MIPS Technologies, Inc)今天宣布,推出其行业标准 MIPS 架构的 Android™ 平台。MIPS 科技还宣布将在 60 天内公开MIPS优化后的源代码。这一举措由若干生态系统合作伙伴共同推动,未来还会有更多合作伙伴加入,将 Android 带给全球广大的 MIPS 开发社区,现在就可以开始采用这一革命性的平台进行数字电视、移动互联网设备(MID)、数码相框(DPF)和

- 关键字: MIPS 数字电视 Android MIPS-Based

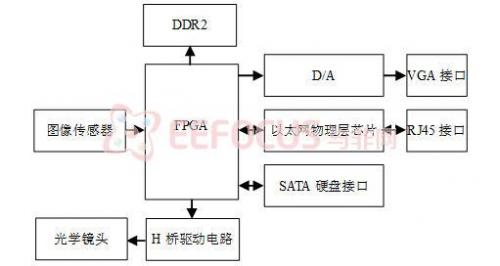

DDR2 SDRAM介绍及其基于MPC8548 CPU的硬件设计(08-100)

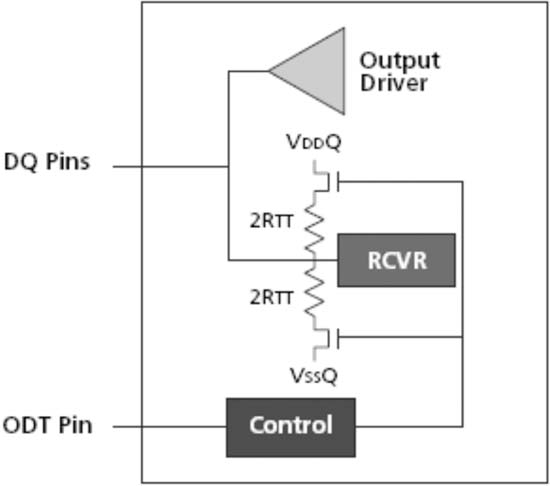

- DDR2(Double Data Rate 2,两倍数据速率,版本2) SDRAM,是由JEDEC标准组织开发的基于DDR SDRAM的升级存储技术。 相对于DDR SDRAM,虽然其仍然保持了一个时钟周期完成两次数据传输的特性,但DDR2 SDRAM在数据传输率、延时、功耗等方面都有了显著提高,而这些性能的提高,主要来源于以下技术的提升:ODT,Post CAS,4n数据预取,封装等。

- 关键字: 思科 DDR2 SDRAM

基于多个特征分块贝叶斯分类器融合策略的人脸识别方法

- 摘要:提出一种基于奇异值分解和贝叶斯决策的人脸特征提取与识别算法。通过对人脸图像样本进行几何归一化和灰度均衡化后,结合分块与加权,运用奇异值分解,分别获得特征脸和标准脸,然后采用多个基于特征分块的贝叶斯分类器(FBBC)的融合策略进行分类识别。实验验证了该方法的有效性,具有良好的精炼和实时性品质指标。 关键词:奇异值分解;贝叶斯决策;人脸特征;分类;图像 引言 人脸识别是指利用计算机对人脸图像进行分析,从中提取有效的识别信息,用来鉴别身份的一种技术,具有直接、友好、方便等优点。基于奇异值特征的人

- 关键字: A Method of Face Recognition Based on the Fusion of Multiple Feature Block Bayesian Classifiers 200810

ADI公司的新一代SHARC 处理器满足专业音频的所有需求

- 极高性能的浮点DSP,比以往的 SHARC处理器性能提高一倍,具有硬件加速器与音频应用提升特性: 片上存储器增加60%以上,提供DDR2 SDRAM外部存储器接口及连接端口 中国 北京——Analog Devices, Inc.(纽约证券交易所代码: ADI),全球领先的高性能信号处理解决方案供应商,最新推出SHARC® ADSP-21469,以帮助开发人员重新定义专业系统中的逼真音响。更多的通道、更多的效果、更多的建模、更高的采样速率:专业数字音频应用正在不断逼

- 关键字: DSP SHARC处理器 DDR2 SDRAM ADI

基于NiosⅡ的图像采集和显示的实现

- 摘 要:采用OV2610的CMOS图像传感器和26K色的TFT液晶屏,在SOPC上集成了OV2610、TFT液晶控制器和DMA控制器,实现了图像数据流的采集和显示。 关键词:DMA Avalon数据流模式 SDRAM 随着大规模集成电路设计技术的进步、制造工艺水平的提高以及单个芯片上的逻辑门数的增加,嵌入式系统设计变得日益复杂。把整个系统集成到一个芯片上,即片上系统SoC(System on Chip)技术是当前嵌入式系统设计的一个研究热点。在Altera公司提供的

- 关键字: SoC DMA Avalon数据流模式 SDRAM

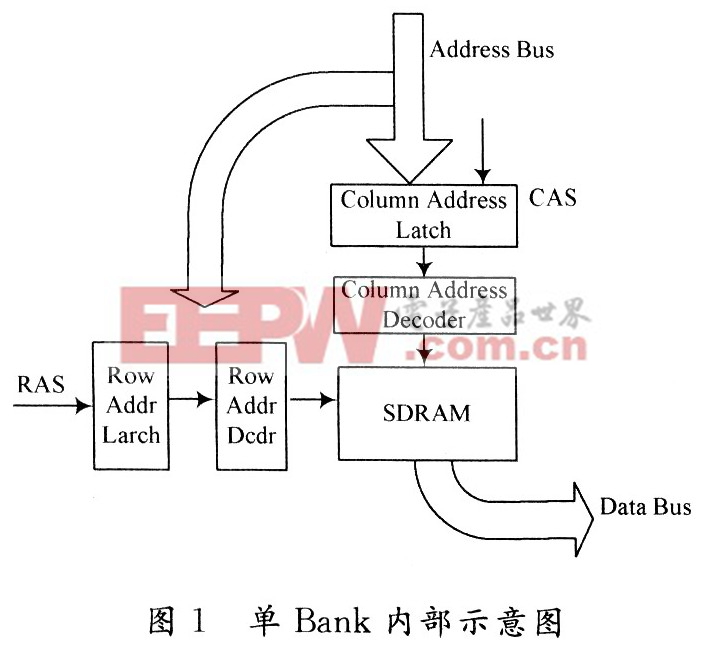

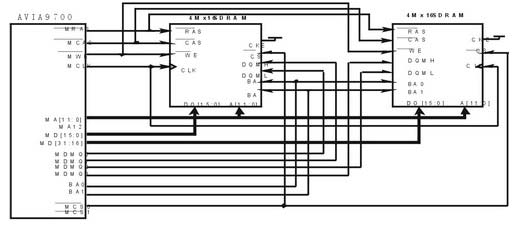

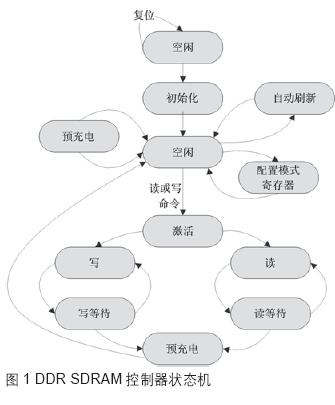

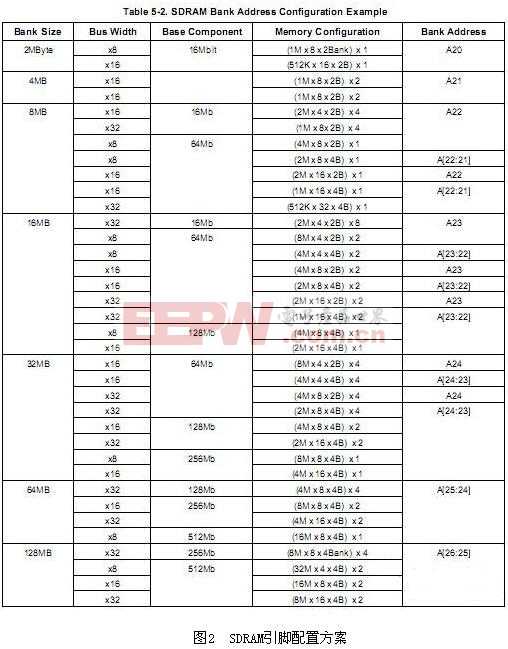

片上SDRAM控制器的设计与集成

- 随着设计与制造技术的发展,集成电路设计从晶体管的集成发展到逻辑门的集成, 现在又发展到IP的集成,即SoC设计技术。SoC可以有效地降低电子信息系统产品的开发成本,缩短开发周期,提高产品的竞争力,是工业界将采用的最主要的产品开发方式。目前国内也加大了在SoC 设计以及IP 集成领域的研究。本文介绍的便是国家基金项目支持的龙芯SoC—ICT- E32 设计所集成的片上SDRAM 控制器模块设计与实现。 1 ICT-E32 体系结构 ICT-E32 是一款32位高性能SoC ,它集成龙芯1号

- 关键字: SoC SDRAM 控制器 MCU和嵌入式微处理器

sdram-based介绍

您好,目前还没有人创建词条sdram-based!

欢迎您创建该词条,阐述对sdram-based的理解,并与今后在此搜索sdram-based的朋友们分享。 创建词条

欢迎您创建该词条,阐述对sdram-based的理解,并与今后在此搜索sdram-based的朋友们分享。 创建词条