- 压控振荡器(以下简称VCO)已经成为当今无线收发器系统中不可缺少的模块, 它是锁相环中最重要的block, 他的噪声性能直接决定了PLL输出相位噪声的噪声性能. 有关PLL整体的分析和设计, 我们将在后期重点讨论. 这里先重点

- 关键字:

设计 VCO 振荡器

- 在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。

无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法

- 关键字:

PLL 电路设计 原理

- 在此说明以晶体振荡器做为基准振荡器,将其与VCO以及PLL电路组合成为信号产生器的情形也被称为频率合成器。

此一PLL-VCO电路的设计规格如表l所示。振荡频率范围为40M~60MHz内的10MHz宽。每一频率阶段(step)宽幅为10

- 关键字:

PLL-VCO 方法

- 电路的功能很多电路都要求把频率准确地倍增,使用PLL电路可很容易组成满足这种要求的电路。例如主振频率为1KHZ,若使用倍增器内插10个脉冲,可变成10KHZ的脉冲信号。在VCO中,即使主振频率发生变化,也能获得跟踪主振

- 关键字:

PLL 10 IC的 频率

- 1 引言 频率源是现代射频和微波电子系统的心脏,其性能直接影响整个电子系统的功能,成为非常重要的部件。 频率源分为二大类:自激振荡源和合成频率源。常见的自激振荡源有晶体振荡器、腔体振荡器、介质振荡器、

- 关键字:

PLL 技术简介 合成 频率源

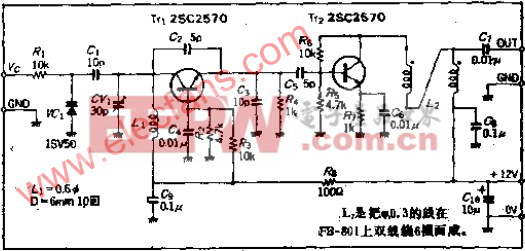

- 电路的功能本电路是50~150MHZ高频电压控制振荡器,可在通信机、信号发生器等高频电路中与PLL电路配合使用。若在控制电压端加4~5V的直流置偏,使话音等信号在这里加权,则可作为FM调制器使用。电路工作原理本电路是高

- 关键字:

工作 原理 功能 电路 高频 VCO 150MHZ

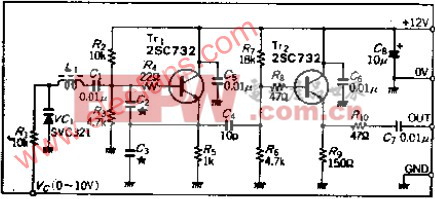

- 电路的功能这是一种可在3M~30MHZ频率使用的电压控制振荡器,在通信机或信号发生器等测量仪器中,可与PLL电路配合使用。振荡回路采用了变形克拉着振荡电路方式,晶体管TR1的参数变动对振荡频率影响不大。电路工作原理

- 关键字:

功能 工作 原理 电路 VCO 30MHZ 高频 频率

- PLL(锁相环)频率合成通过锁相环完成频率的加、减、乘、除运算。该方法结构简单、便于集成,且输出频率高、频 ...

- 关键字:

DDS PLL 电台设计

- Cosmic Circuits,领先的差异化模拟和混合信号IP核提供商,今日宣布其PLL在多个工艺技术节点下经过硅验证。

Cosmic Circuits提供纳米技术节点差异化模拟IP核的广泛组合,其范围覆盖数模转换器、用于无线和音频的模拟前后端平台、电源管理、时钟以及移动行业处理器接口(MIPI)。

系统时钟PLL在55和40纳米工艺技术中实现,并且将为SoC设计者提供各种可供选择的模拟和数字PLL – 包括无需任何外部元件便可支持32 kHz~2000 MHz输入频率的PLL

- 关键字:

PLL MIPI

- 该应用笔记讨论了鉴频鉴相器的指标对锁相环(PLL)死区及抖动性能的影响。在使用电荷泵环路滤波的PLL设计中,通过产生具有最小脉宽的鉴相输出脉冲,可以减轻PLL的死区效应和相关的锁相环抖动。锁相环广泛用于电信行业,

- 关键字:

PLL 鉴频鉴相器 抖动 指标

- 摘要:将DDS和PLL技术结合起来,采用DDS直接激励PLL的混合频率合成方案完成了X波段微波变频信号源的设计,一定程度上解决了频率分辨率、频率转换速度和相位噪声的问题,并完成了实机研制、系统联调试验和测试。结果表

- 关键字:

Band DDS PLL 信号源

- 摘要 锁相环(PLL)是现代通信系统的基本构建模块PLLs通常用在无线电接收机或发射机中,主要提供本振(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数模转换的时钟源。由于每一代

- 关键字:

管理 设计 电源 技术 PLL 基于

- 本文讨论图1所示的基本PLL方案,并考察每个构建模块的电源管理要求。图1.显示各种电源管理要...

- 关键字:

电源管理 VCO LDO 滤波

pll-vco介绍

您好,目前还没有人创建词条pll-vco!

欢迎您创建该词条,阐述对pll-vco的理解,并与今后在此搜索pll-vco的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473